摘要

本文介绍了CMOS- MEMS工艺中使用蒸汽氢氟酸(HF)的释放步骤的表征结果,该结果是通过一种控制CMOS-MEMS器件释放蚀刻工艺的新方法获得的。研究了释放孔尺寸对蚀刻速率和均匀性的影响。对于尺寸在0.48 m2和1 m2之间的释放孔,没有观察到明显的影响。发现晶片内(WIW)均匀性优于3 %,晶片间(W2W)可变性优于2.5 %,同时实现恒定的蚀刻速率0.25m min-1,并保持所需的选择性。新的表征方法基于监测分布在被分析晶片上的一组测试结构的电容值,而不是监控氧化物底切。定义为蚀刻率的新参数通过去除来自与释放工艺本身无关的源的对电容的不期望的贡献,极大地提高了该方法的精度。结果表明,该方法提供的表征精度比基于氧化物横向底切的光学测量的方法高一个数量级。

索引术语—CMOS-MEMS、蚀刻均匀性、蚀刻速率、释放、释放孔、蒸汽HF

介绍

近年来,CMOS电子器件和MEMS器件在单个芯片上的单片集成吸引了很多人

由于其在降低制造成本、更小的尺寸和更低的寄生效应方面的潜在好处而受到关注。实现CMOS-MEMS单片集成的一种方法是使用CMOS工艺的后端(BEOL)层作为MEMS器件的结构层(CMOS-MEMS微机械加工)[1,2]。该方法的关键处理步骤之一是释放蚀刻,其用于释放将形成新MEMS器件的结构,并且是大多数MEMS工艺的基本部分。在该步骤中,从某些区域蚀刻掉牺牲层(通常是氧化硅),以获得正确的器件性能。

释放蚀刻工艺对产量和器件性能有直接影响。尽管过度或不充分的蚀刻可能导致非功能性器件以及随之而来的产量损失,但是不良的释放蚀刻均匀性也可能导致管芯到管芯、晶片到晶片和批次到批次的重要机械和电气器件特性的变化,如电容寄生效应、谐振频率和结构刚度。因此,快速有效的CMOS-MEMS产品开发和工艺控制必然意味着对释放步骤的彻底表征,这对于控制和理解CMOS-MEMS制造过程中的相关产量损失和变化是必不可少的。

在过去的几十年中,已经展示了大量的MEMS器件和技术,但是其中只有一小部分已经达到商业产品阶段。其中一个主要原因是,要成功地将MEMS器件或技术投入生产,需要达到要求的可靠性和成本水平,这通常比演示性能良好的单个原型更具挑战性,也更昂贵。因此,拥有大规模生产可靠性知识的公司不愿意分享他们的可靠性数据和测试方法也就不足为奇了,因为这是他们竞争优势的一部分。因此,与描述新的单个MEMS原型的大量论文相比,几乎没有涉及MEMS可靠性和统计特性的著作发表。CMOS-MEMS工艺和器件的情况甚至更糟:尽管已经使用CMOS工艺的铝层微机械加工制造了许多器件[9–12],但文献中几乎没有关于CMOS-MEMS工艺释放步骤特性的工作。事实上,据我们所知,还没有关于CMOS-MEMS工艺的MEMS释放步骤的统计数据或表征方法被公布。

在本文中,我们展示了CMOS-MEMS工艺中释放步骤特性的结果,并描述了用于获得这些结果的新方法。首先,第二节描述了CMOS- MEMS制造工艺。然后,在第三节简要回顾了几种释放表征方法后,选择了基于电容测量的方法。它涉及第四节中描述的一组电气测试结构,在第六节中描述的释放步骤之后对其进行测量。释放步骤的实验程序已在第五节中介绍过。最后,第七节介绍并分析了获得的结果。特别地,测量了CMOS-MEMS晶片上金属内电介质(IMD)的蒸汽HF (vHF)蚀刻的蚀刻速率和蚀刻均匀性,并研究了不同释放孔尺寸的影响。

图1:典型的0.18 m 1P6M CMOS工艺剖面图

II.制造过程

CMOS-MEMS制造工艺分为三个主要步骤。首先,将晶片作为标准CMOS晶片进行处理。在CMOS工艺过程中,在布局层设计的电子电路和MEMS都是在铸造厂制造的。然后,用vHF工艺释放MEMS器件。最后,MEMS器件被密封、切割和封装。

A.CMOS工艺和针对MEMS释放工艺的调整

CMOS-MEMS结构采用GlobalFoundries的0.18 m 1-Poly-6-Metal CMOS技术实现(工艺截面如图1所示)。6金属选项优于4金属和5金属选项,因为它提供了更大的MEMS设计灵活性。这六个金属层由二氧化硅制成的金属间电介质层(IMD)分隔,并在必要时用钨通孔连接。铝金属化和钨通孔通常用于CMOS节点的BEOL,典型值低至0.18 m [13]。在CMOS处理期间,在每个金属层沉积之前,通常执行晶片的化学机械抛光(CMP ),因此随后的金属沉积是不保形的。

在最后的CMOS处理步骤中,利用焊盘开口掩模,通过钝化层打开MEMS结构上的窗口。这些开口限定了将发生MEMS释放的区域,允许vHF穿透钝化层下面,选择性地蚀刻氧化物而不是金属,从而释放微结构。顶部金属通常用于覆盖(顶层覆盖)MEMS器件,还用作密封层的支撑,如第II-C节所述,密封层可在密封过程中沉积。释放孔在顶部金属上形成图案,以允许vHF渗透。顶层金属的CMOS设计规则对最小释放孔尺寸施加了限制。同时,密封过程的可靠性和简单性在很大程度上取决于释放孔的大小,因为堵塞大孔具有挑战性。在释放过程中,太小的释放孔可能既不允许反应副产物有效逸出,也不允许有效的vHF供应,导致蚀刻速率和/或均匀性的变化。释放孔尺寸对vHF工艺蚀刻速率和均匀性的影响尚不清楚,这是本研究的主要目标之一。

B. 释放:甚高频过程

当牺牲材料是基于二氧化硅时,为了实现释放蚀刻,应用了氟化化学物质[14]。特别是,当需要考虑静摩擦故障,或者需要蚀刻非常小的开口时,vHF释放是释放MEMS器件的首选方法[5]。通过将蚀刻副产物(水)保持在气相中来防止粘着。它还简化了整个释放过程[15],因为它避免了释放后的冲洗和干燥过程,这在使用湿HF释放方法时经常需要。我们已经使用vHF成功地释放了数千个MEMS结构,而没有观察到静摩擦故障。

铝基材料在vHF蚀刻过程中对二氧化硅表现出非常高的选择性。此外,我们已经观察到钨对vHF蚀刻非常鲁棒,并记录在[17]中。前一种材料是我们的MEMS结构的主要成分,因此它们在vHF释放过程中不会被蚀刻。然而,在保持适当的蚀刻均匀性的同时实现高蚀刻速率和良好的选择性是具有挑战性的。例如,蚀刻均匀性和蚀刻速率之间的平衡已有文献记载。

钝化层通常是氮化硅膜。先前已经表明,Si3N4被蒸气HF部分蚀刻(不同于标准的湿HF工艺),并且它形成

厚度增加的残留物[18,19]。残留物可以通过在空气中(或同等条件下)250°C烘烤1分钟来去除。然而,通过如[20]中那样改变氮化物膜的硅含量,可以极大地提高对氮化硅的vHF选择性。在我们以前的经验中,平坦化的富硅氮化物作为vHF蚀刻停止层提供了极好的结果,并且它已经被用于这些实验中。在顶部金属下方,vHF被蚀刻停止层(金属层和通孔)的布置所限制[13]。不幸的是,这种限制不能无限期地阻止甚高频。因此,蚀刻时间不能任意长,否则,一些MEMS特征的不希望的释放将最终发生。

vHF释放步骤可以用已经可用于批量生产的商用vHF蚀刻设备进行[21,22],并且花费不到一个小时,这与总生产时间相比是微不足道的。

C. 密封和包装

一旦释放,MEMS器件可以用铝溅射沉积进行薄膜密封,从而堵塞释放一旦释放,MEMS器件可以用铝溅射沉积进行薄膜密封,从而堵塞释放。

III.释放蚀刻进度

释放蚀刻进度是指在释放过程中已经被蚀刻的氧化物的量,并且它取决于蚀刻时间。在完全可重复的蚀刻过程的情况下,蚀刻相同时间量的两个样品将表现出相同的蚀刻进程。然而,事实并非如此。蚀刻条件,如室压、HF蒸汽流量、酒精蒸汽流量和衬底温度,会影响蚀刻性能[23–25]。此外,牺牲氧化物的成分可能起重要作用,因为成分不均匀性可能转化为蚀刻不均匀性。蚀刻速率测量每单位时间蚀刻的氧化物量。蚀刻均匀性是WIW和

蚀刻过程的W2W重复性。

vHF蚀刻进度可变性可分为来自几个来源的成分:

•管芯到管芯或在晶片内(WIW)

•晶圆到晶圆(W2W)

•逐批

•站点到站点:不同的甚高频蚀刻机

可以通过下面列出的几种方法来测量蚀刻进度:

•SEM检查:通过切割测试结构或MEMS器件(FIB切割或通过破坏晶片),可以直接观察蚀刻过程。这是一个非常准确的方法。然而,它是破坏性的,非常昂贵和缓慢。它在开发层面上造成了时间和成本的限制,并且在生产层面上是不可行的。

•光学检查:蚀刻氧化物的长度可以直接或间接测量[26]。使用诸如悬臂的释放测试结构(一旦下面的氧化物被蚀刻,该释放测试结构就会发生明显的变形)允许间接检查,但是这通常缺乏准确性,并且大量的测量非常耗时。另一方面,直接检查可能更准确,但只能在牺牲氧化物可见(暴露或被透明层覆盖)时使用。幸运的是,在典型的CMOS工艺中,钝化氧化物被一层透明层,即钝化氮化物所覆盖。钝化氮化物(抗vHF)和钝化氧化物都在焊盘和MEMS区域中的钝化开口步骤期间被图案化。在焊盘和MEMS开口边界处,钝化氧化物垂直界面暴露于vHF。在释放步骤期间,暴露的钝化氧化物将被横向蚀刻,并且氧化物底切将随着蚀刻时间的增加而生长。

![]()

![]() 图2:发布过程后测试结构的横截面。IMD氧化物已经被部分蚀刻。两个电极用于测量电容变化。

图2:发布过程后测试结构的横截面。IMD氧化物已经被部分蚀刻。两个电极用于测量电容变化。

例如如图2和3所示。这种欠切可以用来估计甚高频蚀刻速率。通常,光学检查是手动进行的,并接受观察解释。确定蚀刻均匀性需要对蚀刻过程进行高精度的测量,如在第VII-D小节中所示,这不能用氧化物底切的直接光学测量来实现。此外,事实证明,vHF蚀刻在BEOL金属附近的区域被高度催化,使得该过程不是各向同性的,并且取决于存在哪些材料。除此之外,钝化和IMD氧化物可能显示不同的蚀刻速率。因此,在某些情况下,钝化氧化物底切可能不能反映MEMS结构的真实蚀刻进度。

•电容监测:也可以通过对蚀刻结构的电容测量来确定蚀刻进程。鉴于通过SEM图像直接观察蚀刻的氧化物在生产水平上是不可行的,并且钝化氧化物底切的测量可能是不可靠的,并且不可能用于所有的CMOS工艺,电容监测是选择的方法。它基于监控单个控制参数(基于测量的电容而不是蚀刻氧化物的长度),允许简单和精确地确定局部蚀刻进程:将该控制参数保持在规格范围内应该确保与释放过程相关的可预测的产量损失。第四节和第六节介绍了所用的方法,第七节介绍了获得的结果,并与第七节d中的光学方法进行了比较。第七节e中讨论了控制参数的最大和最小限值以及与释放过程相关的MEMS产量损失。

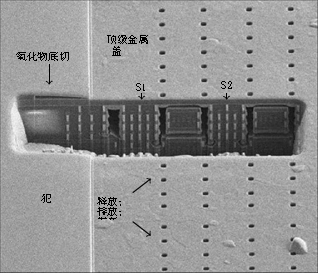

图3:按本文所述制造和发布的MEMS器件的横截面。顶部金属上的释放孔允许甚高频穿透。氧化物横向底切导致悬挂的氮化硅层。支撑封盖的结构(S1和S2)非常类似于本文中设计和测量的蚀刻测试结构。

结论

通过结合晶片探测器和阻抗分析器使用一组测试结构,可以获得快速、自动、广泛和精确的蚀刻进程确定。释放步骤后的电容测量可用于表征应用于CMOS-MEMS工艺的vHF释放工艺的蚀刻速率和均匀性。然而,由于CMOS工艺固有的释放步骤之前存在的电容可变性,仅在释放步骤完成后获取的原始电容值可能不足以进行精确表征。通过使用封闭的测试结构作为参考和定义为蚀刻率(er)的参数,可以消除CMOS工艺的非均匀性影响,这也消除了一些测量误差。这种表征方法提供了比基于氧化物横向底切的光学测量方法更好的一个数量级的精度。它可以应用于CMOS-MEMS器件释放过程的开发和控制。例如,它已成功地应用于评估释放孔大小对甚高频释放过程结果的影响。在这方面,没有观察到明显的影响,因此由CMOS工艺引起的释放孔尺寸变化不会影响蚀刻速率和蚀刻均匀性。根据我们过去的经验,具有极大释放孔(数百微米)的MEMS器件需要与当前器件相似的蚀刻时间,这表明vHF释放工艺

只要释放孔面积大于0.48 m2,蚀刻速率不受释放孔面积的影响。

减压气相HF/酒精蚀刻

对于3个测试的释放孔尺寸,范围从0.48 m2到1 m2的释放孔产生了优于3 %的WIW均匀度和优于2.5 %的W2W可变性。这导致表IV中测试的每个孔尺寸的综合可变性(WIW + W2W)小于3.3 %,假设独立误差,同时实现0.25m min-1的恒定蚀刻速率并保持所需的选择性。甚高频过程

![]()

![]() 对于典型的CMOS-MEMS器件,单次vHF运行的能力指数(cˇ)大于3,大于六适马质量工艺要求的cˇ> 2。

对于典型的CMOS-MEMS器件,单次vHF运行的能力指数(cˇ)大于3,大于六适马质量工艺要求的cˇ> 2。

W2W可变性只能通过更多晶片的实验来精确表征。因此,需要用25个晶片的vHF运行测试来评估完全适合大规模生产的工艺中的变化。

本文介绍的结果和方法对使用类似制造方法的MEMS设计人员非常有用,有助于他们利用这些数据和本文介绍的方法缩短开发时间,减少设计迭代次数。

上一篇: 砷化镓晶片的湿式化学蚀刻

下一篇: 非晶半导体中的光刻工艺