跨晶圆栅极临界尺寸(CD)的一致性会影响芯片与芯片之间在速度和功耗方面的性能差异。随着线宽减小到90 nm及以下,跨晶片CD均匀性的性能规格变得越来越严格。本文提出了一种新的方法,通过光刻和刻蚀工艺顺序来提高跨晶片栅极CD的均匀性。所提出的方法是通过优化整个晶片曝光后烘烤(PEB)温度曲线来补偿光刻工艺顺序中的上游和下游系统CD变化成分。更准确地说,我们首先构建了一个温度-偏移模型,该模型将PEB温度分布与多区PEB板块的设定点偏移相关联。然后从CD扫描电子显微镜测量中识别将跨晶片CD与PEB板的设定点偏移相关联的第二模型。然后基于CD-偏移模型和温度-偏移模型提出了显影后和蚀刻后CD均匀性增强方法。温度-偏移模型被确定为更适合用于CD均匀性控制,因为与CD-偏移模型相比,它具有更好的保真度和便携性。我们证明,在验证实验中,蚀刻后CD变化的标准偏差减少了约1nm,这验证了所提出的CD均匀性控制方法的有效性。

索引术语—约束二次规划、临界尺寸(CD)、临界尺寸均匀性(CDU)、多目标优化、多区域PEB烘烤板、等离子体蚀刻偏差信号、曝光后烘烤(PEB)、过程控制、过程建模。

介绍

如今,批次间和晶圆间的临界尺寸变化一般通过先进工艺控制(APC)来解决。已经对控制晶片老化CD进行了广泛的研究,其方案从前馈到前馈/反馈闭环控制[3]–[ 7]。在这些论文中,CD数据被用于校正来自光刻蚀刻顺序的扰动,以便将晶片平均CD调节到目标,并最小化晶片间和批次间的CD变化。整个晶片的CD可变性变得越来越重要,这要求工艺控制超越批次与批次和晶片与晶片的水平,达到整个晶片的水平,以减少可变性。不幸的是,在现有文献中还没有对跨晶片CD变化的控制进行深入研究。有效控制跨晶片CD变化将导致更紧密的芯片速度和功耗分布。这进而导致更一致的芯片性能和更高的产量。

在整个光刻和蚀刻过程中,各种来源导致CD变化。这些可以如表1所示进行分类。减少跨晶片CD变化的最简单和最直接的方法是使每个处理步骤在空间上均匀。一些研究人员已经研究了提高单个处理步骤的均匀性。Ho等人提出了一种级联控制结构[8],通过控制多区烘烤板的温度分布,将涂覆的抗蚀剂膜厚度不均匀性降低到小于1 nm。向min-展示了坂本的一种新的开发应用技术

图一。光刻工艺控制框架示意图。

尽量减少显影不均匀性,导致晶片CD偏差为6nm(3 sigma)[9]。

然而,对于300毫米晶片加工来说,使每个加工步骤在空间上均匀变得过于昂贵。此外,并不是通过光刻蚀刻顺序的每个处理步骤都提供空间控制权限。我们注意到,在典型的蚀刻工艺中,空间可控性受到严重限制。唯一潜在可用的控制机制是双区ESC冷却系统中背面氦气压力的调节。然而,这种双氦区系统在蚀刻机中并不普遍。此外,由于其仅有的双区配置,背面氦气压力调节在蚀刻过程中提供非常有限的控制权限。光刻步骤提供了更多的空间控制机会。这包括逐个芯片的曝光剂量调整

[10]通过调整加热器区域控制器的偏移和PID设置[12],在曝光后烘焙(PEB)步骤中调整空间温度曲线。这两个控制输入通常很容易接近。我们论文的中心思想是使用这些控制机制,通过补偿其他系统的跨晶片CD变化源,如上游显影不均匀性和下游等离子体蚀刻偏置信号,来改善蚀刻后跨晶片CD均匀性。在这篇论文中,我们把我们的控制行为限制在PEB步骤。曝光设置的探索是一个有待在未来研究中分析的课题。

为了说明我们的方法,考虑图1所示的典型光刻工艺控制框架。因为局部PEB温度可以直接控制局部CD,所以如果通过适当调整PEB温度空间分布可以平衡整个晶片CD变化源,则可以最小化整个晶片的显影后/蚀刻后CD变化1。

通过将PEB温度与多区域烘烤板区域控制器偏移相关联的温度-偏移模型或者将CD与多区域烘烤板区域控制器偏移相关联的CD-偏移模型,可以获得对应于最小化CD扩散的期望PEB温度分布的最佳加热器区域控制器偏移。这些模型是通过一组设计好的实验从实验中提取出来的。还通过平行设计的实验提取了KrF和ArF抗蚀剂的局部光致抗蚀剂PEB热敏性。

如图2所示,在裸硅衬底上涂覆2950 KrF DUV抗蚀剂。光刻工具是一个248纳米波长扫描仪,以及一个现代跟踪功能的多区PEB烘烤板模块。使用最先进的CD扫描电子显微镜(SEM)来测量横跨每个晶片的45个管芯处的线间距光栅上的抗蚀剂CD。

本文的其余部分组织如下。第二节介绍了多区烘烤板和从实验设计(DOE)中提取的经验温度偏移模型和临界尺寸偏移模型。第三节介绍了显影后[即显影检查或(DI)] CD均匀性控制方法以及蚀刻后[即最终检查或(FI)] CD均匀性控制方法。获取基线光刻-蚀刻工艺特征的表征实验和蚀刻后CD均匀性控制的验证实验在第四节中描述。最后,第五部分给出了结论和讨论。

多区域PEB烘烤盘

pEB步骤在控制栅极CD方面变得非常关键,因为热剂量扩散酸并催化曝光后化学放大的抗蚀剂的化学反应。现代晶圆跟踪系统包括一个多区域/多控制器烘烤盘,旨在调整以提供更均匀的空间PEB温度分布。这种多区/多控制器烘烤盘的近似布局,与我们的实验安排相一致,在图3.2中作了概念性的说明

2在本文描述的整个工作过程中,从未获得关于本实验中使用的烘烤板的确切布局或控制算法的信息。所有关于烘烤盘及其操作的信息都是通过实验提取的。

图3。多区域烘烤板上的近似区域位置(通过实验推断)。

在改进的300毫米板上使用200毫米晶片,图3仅显示了300毫米烘烤板的内部200毫米区域。内部200毫米区域由七个区域组成。如(1)所示,在我们的建模方法中,我们假设在多区域/多控制器烘烤板的每个区域上的晶片上的实际稳态PEB温度由温度设定值、区域控制器的相应偏移以及其它区域的影响决定,这是由于烘烤板的良好导电性

其他区域的实际设定值偏移效应(1)

在PEB模块中采用多区域烘烤板的最初动机是减少PEB温度不均匀性,从而最小化其对整个晶片CD变化的影响。然而,在我们的新颖的CDU控制方法中,它被用来产生某些跨晶片的PEB温度分布,以补偿上游和下游的CD变化,使得最终的后显影或后蚀刻CD变化可以被最小化。

温度-失调模型

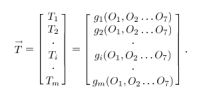

在本文的整个实验部分中,我们只对与multi zone/multi controller烘焙板的200mm区域相对应的内部七个区域的区域控制器偏移进行了实验和建模,而将外部八个区域偏移、曝光剂量、焦距和所有其他参数保留在它们的(标称)基线条件下。在区域控制器偏移的特定组合下,由温度矢量表示的整个晶片的稳态PEB温度可以表示为

烘烤盘校准良好时,变化(通常小于1°C)。该局部线性模型可以通过实验从PEB温度测量值构建,而不需要任何关于板的几何形状或区域控制器算法的额外知识。

其中是区域的控制器偏移,是在每个晶片上测量CD的位置的数量。所示的位置CD是烘烤盘的七个区域偏移的函数,因为每个区域偏移影响整个烘烤盘的PEB温度。一般来说,是一个非线性函数,但是我们也使用线性模型来近似,因为通常烘烤盘在其良好校准附近工作.

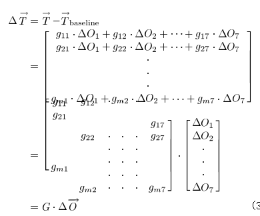

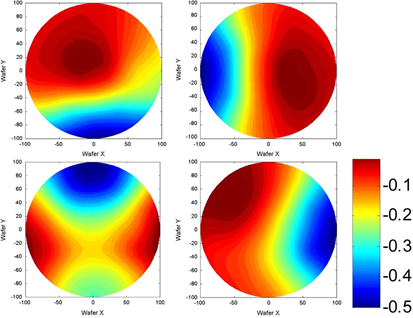

图4。1-3区对稳态PEB廓线的影响(单位:摄氏度)。

通过调节稳态PEB温度分布实现DI CD的可控性

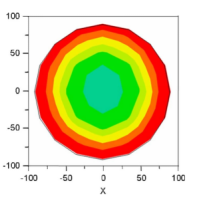

我们提出的CDU控制方法的一个基本假设是,通过多层烘烤板的区域控制器偏移调整来调整整个晶片的稳态PEB温度分布,可以有效地控制整个晶片的DI CD。这通过在设计实验的一次运行中DI CD和PEB温度分布之间的相关性分析来验证,其中故意提高晶片下半平面中的局部PEB温度,以便降低那里的局部DI CD。图10示出了稳态PEB温度与具有0.82的的DI CD强烈相关。

CDU控制和CDU控制方法

A.具有CD到偏移模型的DI CDU控制方法

只要光刻序列中的CD变化源(例如抗蚀剂厚度变化和显影变化)是系统的和稳定的,并且所产生的CD变化是系统的和稳定的,调整多层烘烤板的PEB分布以补偿这些系统的CD干扰并改善CDU是可行的。该方法依赖于通过诸如CD-SEM或散射测量法的计量工具对系统的跨晶片CD变化的精确捕获,以及对多区PEB烘烤板上PEB温度的空间分布的有效控制。

图5。4-7区对稳态PEB廓线的影响(单位:摄氏度)。

图6。区域1–3对跨晶圆DI CD的影响(单位:纳米)。

等离子体蚀刻偏置模型

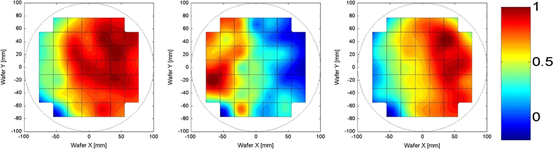

由于等离子体室设计、气流、气压和其他设备设计问题,等离子体蚀刻工艺通常会引起一定的等离子体蚀刻偏置信号。此外,等离子体蚀刻偏置信号通常是稳定和系统的。这里,等离子体蚀刻偏置特征被定义为测量的跨晶片FI CD(蚀刻后CD)和DI CD(显影后CD)之间的差异,其被表示为等离子体蚀刻偏置信号与蚀刻室的晶片蚀刻速率曲线密切相关。图12示出了我们在我们的工业伙伴的制造厂中使用的蚀刻室的晶片上测量的等离子体蚀刻速率曲线。

图12。晶片上的等离子体蚀刻速率分布。

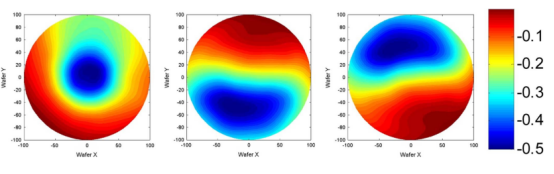

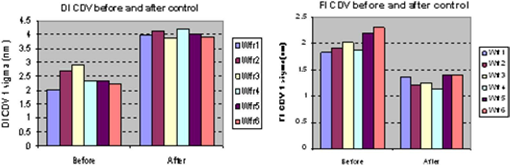

图27。在PEB多区板上应用前馈控制之前和之后,后显影(DI)和后蚀刻(FI) CD分布在六个实验晶片上。

结论和讨论

采用先进的建模和控制技术,通过有意调整整个晶片的PEB温度分布来补偿晶片的变化源,从而提高整个晶片的晶片均匀度。实验构建了多区PEB热板设备模型通过设计的实验,并结合光刻和蚀刻工艺的工艺模型,可以预测最佳的PEB热板偏移设置,以最小化FI CD变化。实验实现了40%的FI CD变化减少,这验证了所提出的方法的有效性。如果集成计量可用,则有望实现额外的FI CD均匀性改善缩短基线表征和PEB热板设置调整之间的时间延迟。

上一篇: 氮化镓的晶体学湿式化学蚀刻

下一篇: KOH溶液中氮化铝的湿化学蚀刻