关键词:碳化硅通孔蚀刻,支柱

引言

研究了电感耦合等离子体刻蚀工艺中线圈射频功率对SiC通孔刻蚀柱形成的影响。据观察,当在反应物中仅使用典型的蚀刻化学物质如SF6时,并且当线圈RF功率降低到一定阈值时,柱密度开始急剧增加。通过适当地修改蚀刻工艺,尤其是反应物混合物,有可能在显著降低线圈RF功率的情况下获得无柱状物的结果。参数空间的这种选择使得晶片能够在SiC通孔蚀刻期间保持在相对较低的温度。这为简化背面工艺开辟了新的选择。

介绍

碳化硅(SiC)作为一种具有高热导率和高温稳定性的宽带隙半导体材料,广泛应用于高功率MMIC。SiC也用作GaN外延生长的衬底,用于更高功率的MMIC器件[1]。在这两种情况下,通常通过器件的背面(通过背面通孔)进行电连接,以进一步改善器件性能。因此,对于基于SiC的器件的制造,无论是直接在SiC上构建的器件,还是使用SiC作为衬底的GaN器件,背面SiC通孔蚀刻都是器件制造的重要部分。

许多先前的研究强调了期望的高SiC蚀刻速率和对蚀刻掩模材料的高蚀刻选择性。在我们最近的研究中,使用SF6蚀刻化学和ICP蚀刻平台获得了约1 μm/min的蚀刻速率和> 25的SiC对GaN的蚀刻选择性[2]。在该研究中,还讨论了与流程可持续性相关的方面,特别是减少支柱。注意到在长时间的室操作下,并且如果室用于蚀刻SiC和GaN,柱的形成通常是影响工艺可持续性的问题。在GaN蚀刻之后或者在腔室经受湿法清洗之后的适当的干燥通常可以减少柱状物的形成。蚀刻前晶片清洗也会对柱状物的形成产生实质性的影响。

在同一项研究[2]中,观察到尽管SiC蚀刻速率随线圈RF功率变化相对较慢,但随着线圈RF功率降低至特定阈值以下,柱状物的形成会显著增加。这种现象也存在,并报道了其他一些蚀刻工艺。为例如,Westerman等人[3]提到,对于GaAs通孔蚀刻,可以通过使用更高的ICP功率、更高的Cl2流量和更低的工艺压力来减少柱状物的形成。这些结果似乎表明ICP功率对柱形成的一般趋势,较高的ICP功率产生较少或没有柱形成。为此,线圈RF功率通常保持在相对较高的水平,以确保无柱蚀刻。

在高线圈RF功率下蚀刻SiC的非预期结果是晶片在蚀刻过程中会变得非常热。这给后端流程集成带来了一定的限制。例如,在典型的背侧通孔形成工艺中,通常使用粘合剂将晶片安装到载体衬底上,器件侧面向载体衬底。晶片的背面被研磨到合适的厚度(通常约100 um)。使用硬掩模对通孔进行构图。然后蚀刻晶片以形成背面通孔。在通孔蚀刻和随后的金属化之后,晶片从它们的载体衬底上分离。

因为在通孔蚀刻期间,晶片被ICP RF功率加热,所以用于将晶片结合到它们的载体衬底上的粘合剂必须能够承受足够高的温度,以避免粘合剂熔化。环氧树脂通常用作粘合材料,因为其粘合强度仅在温度高于177摄氏度时才开始下降[4]。然而,环氧树脂必须被化学溶解,以便将晶片从它们的衬底上分离。这种分离过程可能相当麻烦和冗长。如果可以使用诸如蜡的低温粘合剂,那么将晶片从它们的载体衬底上分离会容易得多。低温粘合剂的使用又需要在相对较低的温度下进行通孔蚀刻工艺。为此目的,在ICP蚀刻期间最小化RF功率将是理想的。然而,如前所述,柱倾向于在降低的RF功率下形成。因此,在降低的RF功率下消除柱状物的形成是有用的。

在本文中,我们报告了我们最近的研究结果,该研究展示了一种新的SiC通孔蚀刻工艺,该工艺大大降低了RF功率,并获得了无支柱的结果。在新的工艺条件下,蜡可以用作粘合剂,将晶片粘合到它们的载体衬底上,而不会引起局部蜡熔化。

实验

具有优化的ICP源的电感耦合等离子体(ICP)蚀刻工具用于实验。对于柱形成研究,首先研磨SiC样品以去除约10 um的SiC,然后抛光以去除另外1 um的SiC。用Ni作为蚀刻硬掩模,将样品图案化以形成通孔图案(通孔直径约60 um)。将样品切成小块(约1cm×1cm大小)并安装在镀镍蓝宝石载体晶片上。首先在固定压板偏压下在各种线圈RF功率下进行蚀刻,以观察线圈RF功率对柱形成的影响。在固定的低线圈RF功率下进行额外的测试,但是改变工艺压力、反应物化学和流速以获得无柱蚀刻结果。在所有情况下,在蚀刻之前对样品进行溅射清洗,以去除留在SiC表面上的任何残留物和潜在的研磨损伤。在某些工艺压力、反应物化学物质和流速下,在低线圈RF功率下获得无柱蚀刻结果之后,将压力和反应物化学物质和流速固定在它们各自的设置,并且进一步降低线圈RF功率,以测试新条件下无柱工艺裕度与线圈RF功率的关系。

还进行了蚀刻速率和SiC对GaN的选择性研究。SiC样品为6H n型SiC。GaN样品是在SiC上生长的GaN。将这两个样品中的每一个的一片(也是大约1cm×1cm)安装在镀镍的蓝宝石衬底上,并用Kapton胶带部分覆盖,以留下未蚀刻的参考区域。同时对所有两个样品进行蚀刻。蚀刻后,移除掩模带并清洁样品表面。使用表面光度仪测量蚀刻和未蚀刻区域之间的台阶高度。在固定的低线圈RF功率下,在各种压板偏压、工艺压力和反应物流速下进行蚀刻。工艺参数的变化被限制在不出现柱的范围内。

结果

支柱形成与RF功率的关系

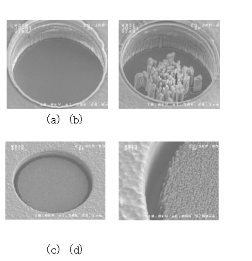

蚀刻测试首先在被称为BKM(最佳已知方法)工艺的高线圈RF功率下进行。在这种蚀刻条件下没有形成柱,图1(a)。然后在后续测试中降低线圈射频功率(但每次测试线圈功率是固定的)。在低线圈射频功率下(BKM设置的45%),出现大量的柱状物形成,如图1(b)所示。在进一步降低线圈RF功率的条件下(BKM设置的32%),通孔蚀刻被完全阻止,见图1(c)和1(d),其中图1(d)是图1(c)所示通孔的放大截面。

图1在(a)高线圈功率下蚀刻的通孔的典型SEM图像;(b)在低线圈功率下,以及(c)更低的线圈功率。图(d)是(c)的放大部分

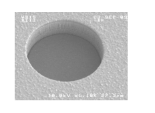

为了在低线圈RF功率条件下获得无柱结果,优化了包括压力、反应物组成和流速在内的其它工艺参数。我们发现改变反应物的组成对柱的形成影响最大。在压力、反应物组成和反应物流速的某些组合条件下,在进一步降低线圈RF功率的条件下获得了无柱的结果。这在图2中示出,图2是在28%的BKM线圈RF功率下蚀刻的通孔的SEM图像。

图2在28%的BKM线圈射频功率下蚀刻的通孔的典型SEM图像,但是在优化的工艺压力、反应物成分和流速下。

蚀刻速率和蚀刻选择性

不仅柱的形成对线圈RF功率敏感,蚀刻速率和蚀刻选择性也是线圈RF功率的函数。在降低线圈射频功率的情况下,蚀刻速率通常会降低。然而,蚀刻速率的降低与线圈射频功率的降低不成比例。例如,当线圈RF与BKM设置相比,功率降低了50%,蚀刻速率从大约1微米/分钟降低到0.8微米/分钟。但是这个蚀刻速率仍然足够高,值得制造。

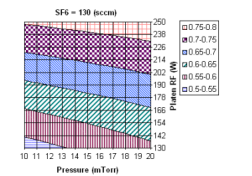

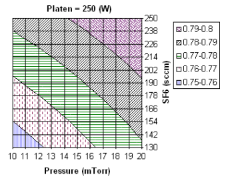

图3在固定SF6流速和低线圈射频功率下,蚀刻速率对压力和压盘射频功率的等高线图。

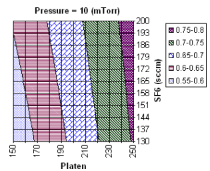

总的来说,如图3和4所示,蚀刻速率强烈依赖于压板RF功率,其中图3是在固定SF6流速(130 sccm)下蚀刻速率作为工艺压力和压板RF功率的函数的等值线图,图3是在固定工艺压力(10毫托)下蚀刻速率作为压板RF功率和SF6流速的函数的等值线图,这两个图都是针对低线圈RF功率的。可以看出,在两种情况下,蚀刻速率随压板RF功率快速变化,但随压力或SF6流速相对缓慢地变化。

图4在固定工艺压力和低线圈射频功率下,蚀刻速率对SF6流速和压板射频功率的等高线图。

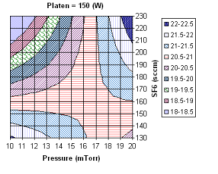

另一方面,SiC对GaN的蚀刻选择性(SiC:GaN蚀刻比)显示出与压力和SF6流速更复杂的关系。这在图6中示出。在该图中,蚀刻选择性的范围从18到22.5(即,SiC∶GaN的蚀刻比从18∶1到22.5∶1)。这对于大多数实际应用是足够的。蚀刻选择性随着压板RF功率的增加而降低.

图5固定射频功率下蚀刻速率对SF6流速和压力的等高线图。

图6在固定RF功率下SiC对GaN的蚀刻选择性对SF6流速和压力的等高线图。

在我们的测试中,我们估计在低线圈RF功率条件下的晶片温度低于80℃。这是根据低温粘合剂(用于将测试样品粘合到其载体晶片上)的蚀刻后外观得出的结论。如果样品温度超过80 ℃,例如在高线圈射频功率下,粘合剂明显熔化,样品冷却后通常会留下小空隙。但是在蚀刻过程中没有粘合剂熔化的迹象。因此,拆卸过程可以大大简化。

结论

在较大的线圈射频功率范围内,SiC刻蚀速率随着线圈射频功率的降低而缓慢降低。然而,蚀刻速率随着台板射频功率的增加而迅速增加。SiC对GaN的蚀刻选择性随着线圈RF功率而增加,但是随着压板功率而降低。在高线圈RF功率下,柱状物的形成通常会减少,并且当线圈RF功率降低到某一阈值时,当在反应物中仅使用典型的蚀刻化学物质如SF6时,柱状物的形成会成为真正的问题。然而,通过改变反应物混合物和流速,显示出线圈RF功率可以显著降低,并且仍然获得无柱的结果。改进的蚀刻工艺允许使用低温粘合剂来大大简化通孔形成工艺。

上一篇: 铜薄膜在含HF清洗液中的腐蚀行为

下一篇: O极和Zn极ZnO单晶的蚀刻行为