Abstract

The effffects of difffferent surface preparations on NiPtSi thermal stability were studied. HF wet clean, argon sputter etch and remote plasma pre-clean were used as silicide pre-cleans prior to NiPt sputter deposition and subsequent silicidation on blanket and patterned Si wafers. NiPtSi was characterized using SIMS, ellipsometry, voltage contrast (ES25) testing and electrical performance measurements of 65 nm test structures. Results show that when an in situ remote plasma pre-clean is used in addition to a classical HF wet clean to remove native oxide from the Si substrate prior to NiPt deposition and silicidation, Rs uniformity and SRAM electrical performance as a function of thermal budget are signifificantly improved. Rs measurements of patterned wafers and SIMS analysis of blanket wafers strongly suggest that the absence of native oxide prior to NiPt deposition and the presence of flfluorine at the NiPtSi/Si interface play a key role in improving NiPtSi thermal stability.

1. Introduction

NiSi has replaced CoSi2 and TiSi2 in 65 nm and smaller node technologies because of three relative advantages: lower silicon consumption, linewidth-independent low resistivity and low thermal budget. This last feature can also be a drawback because it translates into poor thermal stability of the nickel monosilicide phase. NiSi thermal instability means that, given a suffiffifficient thermal budget, Ni diffffuses in an uncontrolled manner under the transistor gate, either during the silicidation step or during subsequent interconnect manufacturing stages. This unbridle diffffusion of Ni is called encroachment or piping, and can result in excessive current leakage between the source and drain areas and in the entire silicon well. Ultimately, encroachment leads to poor device yield.

The use of nickel alloys, such as NiPt, has been found to improve NiSi’s thermal stability [1,2]. The proper choice of surface preparation prior to silicidation can further improve NiPtSi thermal stability. The work presented in this paper focuses on the effffects of difffferent surface preparations on NiPtSi thermal stability. Results show that performing an in situ remote plasma silicide pre-clean after a standard HF wet clean improves NiPtSi Rs uniformity and thermal stability. Possible mechanisms underlying these effffects are presented in Section 5.

2. Experimental methodology

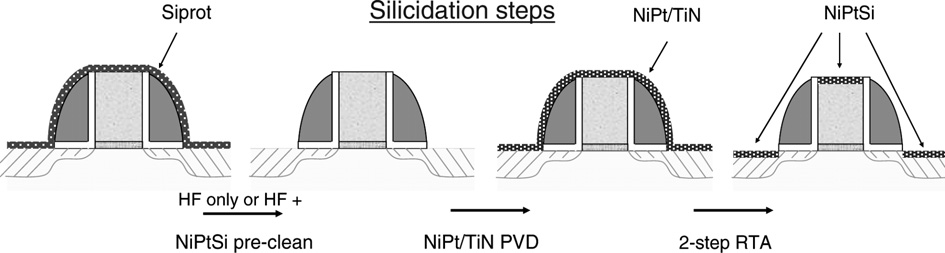

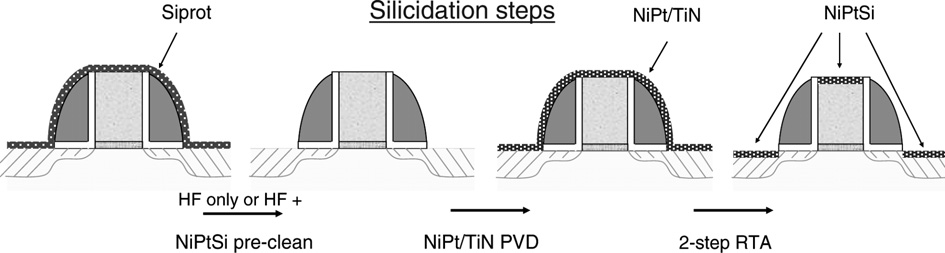

Three difffferent pre-silicide surface preparations were used in this study to remove oxide from the Si substrate prior to NiPt sputter deposition: an ex situ dilute HF wet clean (0.5–2% in H2O), an in situ argon sputtering etch (SSE or soft sputter etch), and an in situ remote plasma clean (RPC). Blanket wafers and patterned wafers with 65 nm technology devices were processed using one or a combination of these pre-silicide cleans. To form the silicide, Ni(5%)Pt was sputter deposited on the wafers followed by a TiN capping layer. A two-step RTA was then performed to form the silicide.

2.1. Blanket wafer preparation

Four difffferent surface preparation combinations were used: HF only, HF + Ar sputter, RPC only and HF + RPC. The HF wet etch was carried out in a dedicated tool (ex situ). Ar sputter and RPC took place in the NiPt deposition tool (in situ). Wafers were transferred from the in situ pre-clean chambers into the sputter deposition (PVD) chambers under UHV (10 8 Torr). A 9–10 nm NiPt layer was deposited fifirst, followed by a 10 nm thick TiN capping layer. The wafers were then annealed using a two-step RTA process consisting of a fifirst RTA1 step to drive the NiPt into the Si substrate, a selective etch step to remove the TiN capping layer and any unreacted NiPt, and a second RTA2 step to form the NiPt monosilicide phase. Transformation curves were created by annealing various wafers at difffferent temperatures during RTA1.

2.2. Blanket wafer tests

2.3. Patterned wafer preparation

2.4. Patterned wafer tests

The ES25 voltage contrast technique was used to detect morphological instabilities of the silicide shortly after silicidation. Ellipsometry was used to measure the thickness of NiPtSi after RTA2 in undoped areas of the wafer, having no structures, called Tboxes. Electrical tests were performed to measure the effffects of the difffferent surface preparations on the sheet resistance of active and poly silicon. SRAM standby leakage current and electrical fails were measured before and after additional 400 C thermal anneals.