在大直径硅上外延集成第三族氮化物半导体的梦想正在被完全实现,这是由硅上氮化镓技术在提高效率的同时大大降低固态照明和电力电子的制造成本的巨大潜力所驱动的。在硅衬底上生长高质量的氮化镓是非常具有挑战性的,因为氮化镓和硅之间的热膨胀系数(CTE)和晶格常数之间存在巨大的失配,经常会在氮化镓薄膜中产生微裂纹网络和高密度的穿透位错。铝成分分级的AlGaN/AlN缓冲层不仅被用来在高温生长期间建立压缩应变以补偿冷却期间产生的拉伸应力,而且还滤除了TDs以在硅衬底上实现无裂纹的高质量n-GaN膜,对于(0002)和(101N2)衍射,X射线摇摆曲线线宽都低于300弧秒。在硅上氮化镓模板上,在去除p-AlGaN和p-GaN层之前,高质量的InGaN/GaN多量子阱(MQWs)过度生长了精心设计的V型缺陷,有意引入这些缺陷以屏蔽作为非辐射复合中心的TDs,并增强空穴通过类通孔结构注入到MQWs中。在去除外延硅(111)衬底后,将生长好的氮化镓基发光二极管晶片加工成具有反射p电极和粗糙化N面表面的垂直结构薄膜发光二极管芯片,以提高光提取效率。

实验

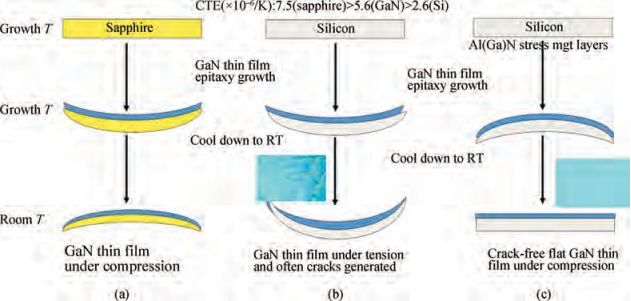

目前氮化镓基发光二极管行业最流行的技术方法是在蓝宝石衬底上生长氮化镓。尽管蓝宝石衬底晶格不匹配,但两步生长技术[1]可以实现通常在压缩应变下的高质量氮化镓薄膜,因为蓝宝石的热膨胀系数(CTE)大于氮化镓(图1(a)),提供了相对较宽的工艺窗口,形成微裂纹的风险很小。在大直径硅衬底上外延生长氮化镓基发光二极管在显著降低高能效固态照明的发光二极管制造成本方面具有巨大潜力。然而,这种外延集成受到两大技术挑战的阻碍。氮化镓和硅之间17%的晶格失配通常会导致高密度(109-1010厘米-2/线)位错(TDs),通常作为非辐射重组中心工作,因此降低了发光二极管的效率。由于巨大的CTE失配(54%),外延生长后的硅衬底落后于生长温度冷却期间晶片收缩的氮化镓,并有效拉伸氮化镓膜,这可能导致拉应力、晶片弯曲和氮化镓层中微裂纹网络的形成(图1(b))。应该提到的是,即使是名义上无裂纹的GaN-on-Si LED外延晶片在生长后立即产生的强残余拉伸应力,在长时间工作下仍然经常会产生微裂纹,导致载流子泄漏、光输出衰减和其他可靠性问题。

图1 (彩色在线)生长和冷却期间生长在(a)蓝宝石和硅衬底上的氮化镓薄膜(b)没有和(c)具有铝成分分级的AlGaN/AlN缓冲层的应力演变示意图

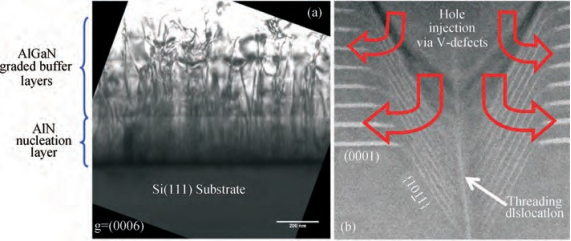

图2 (彩色在线)GaN-on-Si LED外延膜的截面TEM图。(一)铝成分渐变的AlGaN/AlN/Si界面区。InGaN/GaN多量子阱区

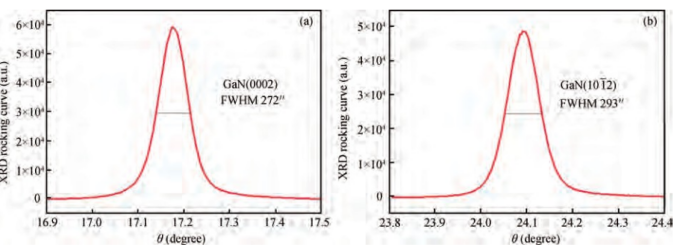

图3 (彩色在线)在硅(111)衬底上生长的3.6微米厚的n-GaN([硅]掺杂8×1018cm-3)的(0002)和(101N2)衍射的双晶体X射线摇摆曲线

我们发现,在铝成分分级的AlGaN/AlN缓冲层中建立的压缩应变不仅可以用来补偿冷却过程中由于CTE引起的拉伸应力,而且根据截面透射电镜观察,还可以诱导界面处的穿透位错的倾斜和消失(图2(a))。生长在硅(111)上的3.6-微米厚无裂纹n- GaN(硅掺杂8×1018cm-3)薄膜的GaN(0002)和(101N2) X射线摇摆曲线的半峰全宽(FWHM)分别为272和293弧秒(图3),两者相当类似于生长在平坦蓝宝石衬底上的氮化镓。GaN(0002)和(101N2) XRCs的窄半高宽表明,生长的GaN-on-Si材料具有降低的TD密度。应该指出的是,氮化镓(0002)和(101N2) XRCs FWHMs之间的微小差异反映了有限密度的边缘型位错,这些位错通常是发光二极管中的非辐射再聚合中心。

类似于生长在平坦蓝宝石衬底上的氮化镓。GaN(0002)和(101N2) XRCs的窄半高宽表明,生长的GaN-on-Si材料具有降低的TD密度。应该指出的是,氮化镓(0002)和(101N2) XRCs FWHMs之间的微小差异反映了有限密度的边缘型位错,这些位错通常是发光二极管中的非辐射再聚合中心。

硅基氮化镓发光二极管薄膜垂直芯片工艺

具有相对窄带隙的硅衬底可以吸收从工作发光二极管的铟-氮化镓/氮化镓多量子阱发射的大部分蓝色光子。由于氮化铝层的电阻,具有硅衬底的硅上氮化镓发光二极管在非常高的电压下工作,并给出非常低的光输出.为了获得高效的硅上氮化镓发光二极管芯片,必须去除外延硅衬底,在此之前,作为机械支撑的导电硅载体晶片和电流路径应该用金属叠层结合到硅上氮化镓发光二极管晶片的p侧表面。P-氮化镓表面和硅载体之间的金属叠层包括晶片键合金属层和银基反射P电极,其用作与P-氮化镓表面的镜像和P型欧姆接触。在去除硅外延衬底和蚀刻掉氮化铝/铝镓缓冲层之后,用氢氧化钾溶液粗糙化氮面氮化镓表面以增强光提取,随后进行氮电极制备。最后,处理过的晶片准备好进行硅载体研磨和芯片切割和分类。垂直结构薄膜芯片工艺如图5所示,可能适用于表面等离子体增强和柔性发光二极管封装应用。图6展示

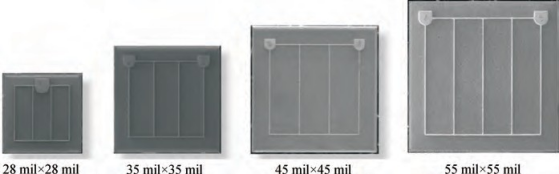

图6 一系列硅基氮化镓发光二极管薄膜芯片产品的扫描电镜图像

总结

我们开发了外延生长、芯片加工和封装技术。特别是,铝成分分级的AlGaN/AlN缓冲层已经成功地用于解决CTE失配和GaN与Si之间的晶格匹配,在Si衬底上获得无裂纹的高质量GaN膜,具有很好的再现性和一致性。在多量子阱有源区中有意引入了v型缺陷,大大提高了IQE和空穴注入效率。采用薄膜垂直芯片结构,提高了接近朗伯分布的氮化镓基发光二极管的光提取效率。晶圆级磷光体技术应用于硅上氮化镓发光二极管,在芯片切割前将蓝色光子转换为白光输出。我们已经将硅上氮化镓发光二极管商业化,在350毫安的注入电流下,1平方毫米芯片的平均效率为150–160流明/瓦,这对于定向照明应用具有内在优势。

上一篇: 通过紫外线辅助光蚀刻技术实现的湿式蚀刻

下一篇: 化学镀NiP-Pd沉积过程中铜和镍的腐蚀