集成电路的历史背景

尽管晶体管已经微型化,但电子电路的初始尺寸仍然相当大,而减小整体电路尺寸、重量和功耗,以及提高性能仍然是电子学研究的主要目标。由于由不同材料和制造工艺制成的各个组件,每个组件都需要通过焊接连接,而焊接是劳动密集型的,并且阻碍了电子电路的微型化。基尔比提供了一种替代方法来应对这一挑战,通过减少使用的材料和制造工艺的数量。基尔比的解决方案是在单个材料块内制造所有组件,因为其他组件,如电阻器和电容器,可以由半导体制成。新的电路设计允许组件按顺序加工,并且可以更紧密地排列在一起,具有更少的复杂互连和故障机制。

光刻技术:历史、未来和挑战

在集成电路开发之后,制造工艺发生了巨大变化。制造工艺分辨率的提高一直是主要驱动力,因为更好的分辨率允许电子元件的微型化,这导致每个晶片上有更多的芯片、更小的电路尺寸和更高性能的设备。此外,更好的分辨率提高了生产率,从而降低了成本。因此,制造工艺需要具备在高分辨率、产量和吞吐量方面形成复杂结构的能力。光刻技术一直是主要的图案化工艺,直到最近一直满足集成电路制造工艺的严格技术要求。

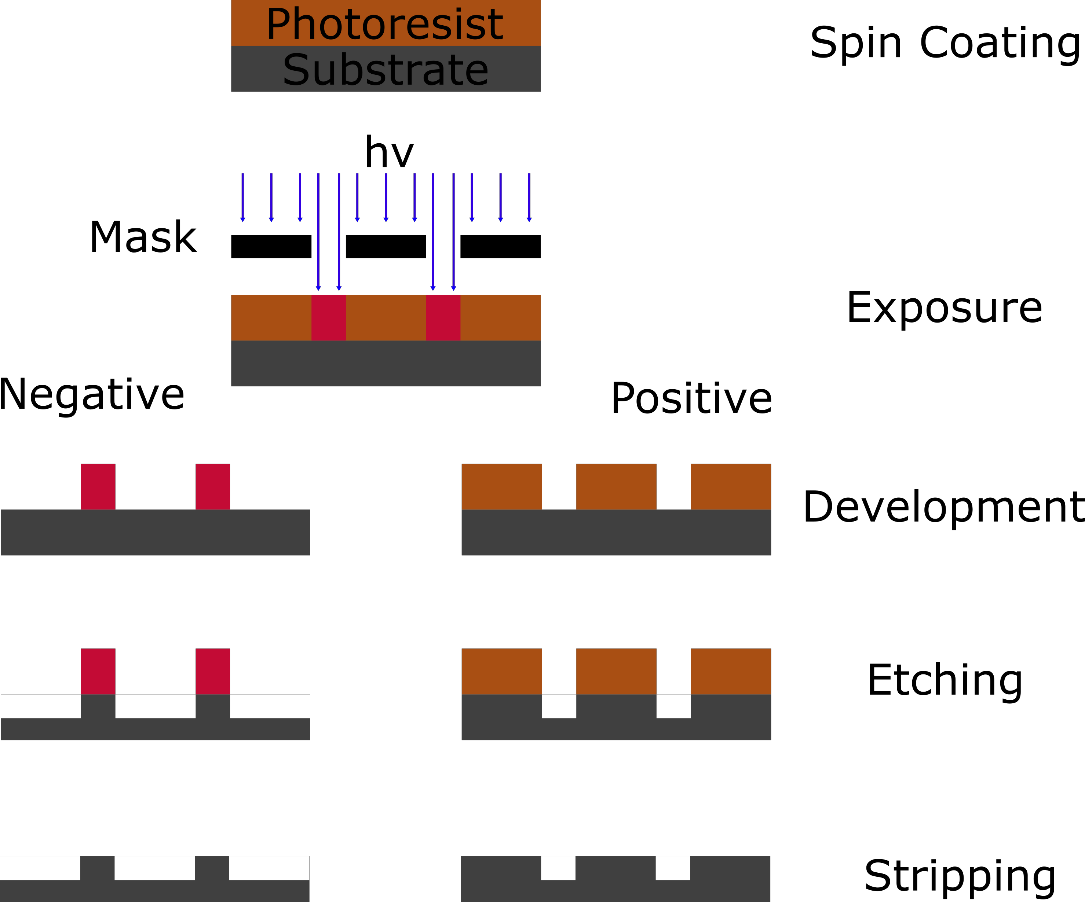

图1 光刻工艺的示意图。准备一个旋转涂覆的基底。通过未遮盖区域选择性地照射光敏电阻。正面光敏电阻在受光区域变得可溶,而负面的光敏电阻在受光区域变得不可溶。在显影过程中,可溶性光敏电阻被洗掉,蚀刻步骤将图案转移到器件材料中,并可以去掉光敏电阻以留下图案化的电路。

图1.显示了光刻工艺的一般过程的示意图。将刻有电路图案的掩膜放置在涂有光敏电阻的基底上。通过掩膜对光敏电阻进行曝光,暴露的区域发生化学变化。如果它是负光敏电阻,暴露区域变得不溶;如果它是正光敏电阻,暴露区域变得可溶。然后,将光敏电阻浸入开发溶液中,溶解可溶区域,通过使用剩余的光敏电阻作为蚀刻屏障,将掩膜上的图案复制到基底上。基于这些基本概念,光刻工艺发展成为具有最高分辨率、最精确的图案化工艺。

图2 接触点、接近度和投影打印的概念示意图

在曝光步骤中,光刻工艺从接触式印刷发展到接触式印刷,以保护掩膜免受接触(图2)。接触式印刷工艺进一步发展为投影式印刷,以缓解近场衍射引起的分辨率限制。虽然图1.2只强调了几项改进的装置,但光刻工艺中还有很多其他的升级。

例如,随着芯片变得更加复杂,掩膜制作工艺也取得了进步。随着分辨率要求的不断提高,缩微照相技术被开发出来,它在晶片上打印一个缩小的图像。缩微照相技术消除了制作1:1掩膜的需要,但需要一个额外的步骤,将缩小的图像对准晶片,因此不可避免地需要改进计量学。此外,随着分辨率和图像面积的增加,这个新工艺给镜头制造带来了负担,需要大幅增加镜头尺寸和复杂性。最后,为了获得更好的分辨率,改变照明源是必要的,这需要改变光学材料、光敏电阻材料、化学和工艺以及改进的开发工具。

极紫外光(EUV)光刻是下一代光刻技术之一,它遵循了上述发展过程,并面临一些前所未有的挑战。EUV光刻通过使用软X射线波长来提高分辨率。首先,EUV光刻工具必须在高真空下运行,并且只包含反射光学元件(包括掩膜),因为EUV波长不能穿透任何介质。由于每个EUV反射表面吸收约30%,因此需要创建高功率的EUV光源。由于来自高功率EUV源的光子会严重加热工具,膜片和从真空提取热量的热稳定性提出了工程挑战。可以看出,光刻技术的改进是一个挑战,因为光刻工具中的每个组件都是相互连接的。

紫外纳米压印光刻技术:背景和亮点

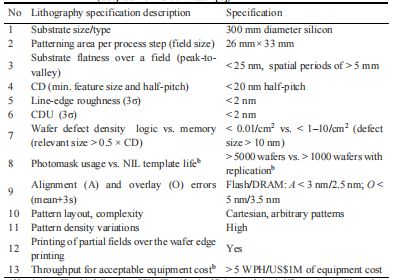

表1.1确实列出了新光刻技术要成为先进半导体集成电路可行制造选项所需满足的复杂要求。这些要求包括但不限于高分辨率、高生产效率、高可靠性和成本效益等。

表1 具有代表性的半导体集成电路制造要求。对于特定的设备和设备层,实际的需求可能会有所不同。这些是对高级内存的近似估计,包括Flash和DRAMa

对于过去的50年,光学光刻确实是半导体行业的主要图案化工艺。然而,随着技术的发展和芯片尺寸的不断缩小,光刻技术面临着越来越大的挑战。即使有了193i光刻技术,仍然存在衍射极限等物理限制,这限制了其最终分辨率。

为了克服这些限制,行业一直在探索其他高分辨率光刻技术。例如,EUV光刻技术被认为是一种具有突破性的技术,因为它使用极紫外线的波长,这比传统的可见光和紫外线的波长更短。这使得EUV光刻有可能提供更高的分辨率,从而满足先进半导体集成电路制造的需求。

然而,即使有了这些新的技术,也需要克服许多工程和技术挑战,例如光源的稳定性、掩膜的制造和成本、以及与现有制造工艺的兼容性等。因此,新的光刻技术需要满足一系列复杂的要求,才能成为先进半导体集成电路制造的可行选项。

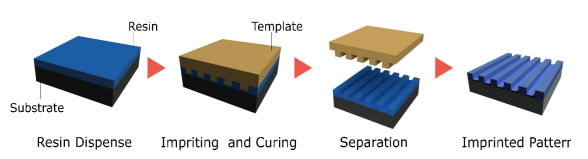

虽然研究人员提出了几种纳米图案技术,但EUV光刻和紫外线纳米压印光刻(UVNIL)是具有商业潜力的半导体生产技术[8]。纳米压印光刻(NIL)是一种新兴的技术,是一种有效的低成本纳米级图案制作方法,是解决光刻实际限制的有前途的解决方案。图1.3示出了NIL的一般过程。在压印之前,将压印抗蚀剂施加到基片上。模板掩模降低到抗蚀剂的单体液滴上,液滴通过毛细作用扩展并填充掩模中的浮雕图案。抗蚀剂液滴合并并完全填充模板上的特征。在固化后,光固化或热固化聚合物抗蚀剂会复制图案。模板掩模被移除,在基片上留下压印的抗蚀剂。理想情况下,压印的抗蚀剂完全与原始模板一致。然后,该图案可用于进一步加工,例如反应离子刻蚀。NIL工艺为大规模生产纳米级特征提供了一种低成本的方法,并有可能成为未来集成电路制造的关键纳米光刻方法。

图3 与NIL过程所涉及的步骤。图案掩模被压在抗蚀剂膜上。在固化和分离步骤之后,将印迹抗蚀剂留在基板上,用于进一步处理

上一篇: 硅湿蚀刻的建模、仿真和校准

下一篇: GaN基micro-LED的特性与技术