介电损耗是超导量子比特的主要退相干源之一。目前,高相干性超导量子比特主要由低介电损耗基底上的超导薄膜组成的材料系统形成,其中损耗主要来源于表面和界面。在众多候选材料系统中,氮化钛(TiN)薄膜与蓝宝石基底的组合具有良好的潜力,因为它具有抗氧化的化学稳定性和高质量的界面。在这项工作中,报告了一种沉积在蓝宝石基底上的TiN薄膜,该薄膜在材料界面处实现了低介电损耗。通过对具有相同批次TiN基础层但具有不同几何形状和不同材料界面参与比例的量子比特分流电容器的一系列传输量子比特进行系统的表征,定量提取了在基底-金属界面处小于8.9×10−4的损耗正切值。通过优化传输量子比特的界面参与比例,可重复地实现高达300微秒的量子比特寿命和接近800万的质量因子。证明了蓝宝石基底上的TiN薄膜是高相干性超导量子比特的理想材料系统。分析进一步表明,电路中约瑟夫森结部分周围的界面介电损耗可能是最先进的传输量子比特寿命的主要限制。

介绍

在超导量子计算中,与操作时间尺度相比,足够长的量子比特相干时间是实现实用量子计算的基石。在过去的二十年里,通过量子比特设计的创新以及退相干源的缓解,超导量子比特的相干时间已经提高了五个数量级以上。在众多的退相干通道中,介电损耗被指出是普遍存在的,并且已经成为几个关于传输平台相干时间突破的中心。

为了降低介电损耗,Pi和tan δi是两个独立的变量,可以进行优化。然而,由于PR与量子比特几何之间的强相关性(稍后将讨论),Pi的优化可能会带来与设备结构、尺寸和测量配置有关的潜在折衷。因此,降低与材料和制造相关的界面tan δi值是降低介电损耗的一般和基本方法,尽管具体的量子比特设计可能会有所不同。除了在社区广泛使用的铝(Al)膜在硅基底上外,人们还积极探索了其他材料系统和相应的制造工艺以降低介电损耗。例如,钛氮(TiN)膜在硅基底上的各种设备中进行了探索。最近,一项关于钽膜在蓝宝石基底上的研究报告了二维(2D)传输门量子比特中的低介电损耗。使用铌膜在硅基底上制造的长寿命2D传输门量子比特已作为敏感探针应用于表征其他耗散机制。在这些先前的研究中,通过利用高质量的材料系统和优化相应的制造工艺,实现了5×10^6范围内的量子比特质量因子。要进一步改善量子比特的寿命,需要对电路中的损耗机制及其与底层材料性质之间的对应关系有定量的理解。

设计和制造

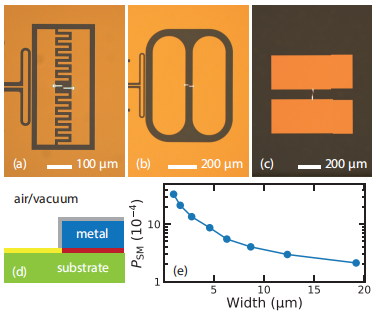

SSM是SM接口的积分限,由超导金属的几何形状决定。在我们的传输门量子比特设计中,我们应用了不同PSM制度下量子比特分流电容的不同几何形状。对于PSM值较大的2D传输门量子比特,我们选择了能够将更多能量分布在SM接口区域中的数字几何形状。我们保持间隙和手指的宽度相同,并将它们一起变化以减少我们设计的数字电容中的变量数量。手指的数量和长度相应调整,以实现电容的目标值。同时,在PSM较小的制度下,我们使用分流电容的哑铃形几何形状的2D传输门量子比特。我们研究中获得的最小PSM是通过将哑铃形几何形状与3D配置相结合来实现的。上述不同几何形状的传输门量子比特如图1(a)-(c)所示。

图1 (a)-(c) 本研究中典型的数字2D、哑铃2D和哑铃3D传输门量子比特的显微镜图像。黄色区域是TiN基底层。深色区域是蓝宝石基底。图像中心的白色区域是Al/AlOx/Al约瑟夫森结。

(d) 超导金属和基底横截面的示意图。绿色、蓝色和白色区域分别代表基底、超导金属薄膜和空气/真空。黄色、红色和灰色区域表示SA、SM和MA界面上的潜在损耗层。插图未按比例绘制。

(e) PSM随数字分流电容的间隙和手指宽度的变化而变化。

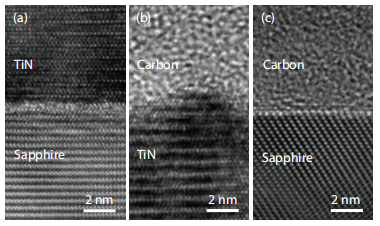

为了获得模拟PSM所需的参数,我们使用透射电子显微镜(TEM)对TiN膜在蓝宝石基底上的横截面进行表征,并在图2中展示结果。SM接口的图像表明,在高度结晶的TiN膜和蓝宝石基底之间存在一个薄而混乱的层。通过假设SM界面上的损耗是由这个混乱层引起的,我们采用了它的平均厚度(约1纳米)作为tSM。在TEM图像中,混乱层显示出与蓝宝石基底相似的对比度,这意味着该层的主要成分可能是AlOx。因此,我们使用蓝宝石的介电常数(10.15 ε0,其中ε0是真空介电常数)作为εSM。作为许多金属氧化物的典型值,在PR的模拟中广泛采用了大约10 ε0的εSM。

图2 蓝宝石衬底上氮化钛薄膜的SM、MA和SA界面的(a)-(c) TEM图像。注意在(a).中,氮化钛薄膜和蓝宝石衬底之间的厚度约为1 nm的无序层虽然(c)有不同的对比,但SA界面上的蓝宝石原子通常位于预期的晶格位置。在(b)和(c)中,沉积碳覆盖层用于TEM样品的制备。

结果与讨论

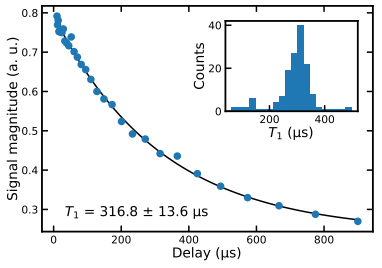

我们使用标准T1测量来表征我们的传输门量子比特。为了减少量子比特性能时间波动的潜在影响,我们重复测量大约100次,并使用平均T1作为数据分析的代表性值。典型的测量结果如图3所示。量子比特的弛豫通常表现出预期的单指数衰减行为,而T1的统计分布相对集中。在我们的系统测量中,对5种类型的芯片上的13种不同PSM值的传输门量子比特进行了测试。对于每种类型的芯片,我们从相同的晶圆中随机挑选多个样本进行测量,以检查再现性。在我们的最佳设备上,测量的时间平均弛豫时间T1为291.7±68.6微秒。

图3 典型的T1测量结果。蓝色的圆圈是实验数据点。黑色曲线是单次指数衰减的拟合结果。拟合结果为T1 = 316.8µs,拟合误差为13.6µs。插图显示了t1在大约100轮连续测量中的直方图分布。

关于tan δSM ' 8.9 × 10−4的拟合结果,我们想要指出的是,这个值设定了SM界面介电损耗的上限。我们的模拟结果显示,PSA和PMA与PSM大致成正比,尤其是在使用数字分流电容的情况下,这与之前的研究一致。因此,SA和MA接口的潜在介电损耗归因于tan δSM的拟合,导致结果大于其实际值。虽然tan δSM的提取值被高估了,但它表明TiN薄膜的SM界面的质量与具有低介电损耗的最佳报道材料系统相当。