三维设备集成通过在多个层之间分配控制线、量子位和谐振器等元件,促进了由数十个量子位组成的超导量子信息处理器的构建。在倒装芯片键合的多芯片模块中,谐振器和量子位的频率取决于其附近导体和介电体定义的电磁环境的细节。因此,准确的频率定位需要精确控制芯片之间的间距,并最小化它们的相对倾斜。在这里,我们描述了一种使用聚合物间隔物来控制芯片间间距的方法。与没有间隔物的相同工艺相比,我们将测量的平面度误差降低了3.5倍,平均倾斜度为(76±35)µrad,与目标芯片间间距的偏差降低了10倍,平均为(0.4±0.8)µm。我们将此工艺应用于共面波导谐振器样品,并观察到芯片间谐振器频率变化低于50 MHz(≈1%)。我们在单光子水平上测量的内部质量因子为5×10^5,这表明添加的间隔物与低损耗器件制造兼容。

一、介绍

量子计算在材料科学和量子化学中实现复杂多体量子系统的模拟方面显示出巨大的潜力。要解决实际问题,需要成百上千个近乎完美的量子比特(qubits),因此需要可扩展的实现。超导电路是满足这一标准的领先实现之一。由于量子比特的相干时间有限和控制的准确性,将需要基于表面码[4, 5]等的量子误差校正,这将需要数百万个物理量子比特(取决于量子比特错误率和噪声模型假设)。制造如此数量的量子比特仍然是一个艰巨的工程挑战,并将需要创新的制造技术,例如倒装芯片键合,将多个平面(单层)芯片组合在一起和通过超导穿孔通到衬底,以抑制包装模式。虽然空气桥交叉可以克服一些路由挑战,但平面设备仍然受到相邻信号迹之间可接受的串扰的限制。相反,多芯片方法最终将更加有效,因为电路元件(量子比特、耦合器、读出谐振器等)可以放置在具有优化制造程序或不同材料平台的单独芯片上。

在倒装芯片键合中,两个图案化的设备通过超导金属的凸块面对面连接,通常使用铟,因为它具有延展性并且易于冷焊接。芯片间间距d是一个关键参数,因为它影响谐振特性的频率、不同信号线之间的阻抗匹配以及元件之间的电容和电感耦合率(例如,用于量子位-量子位耦合器或量子位-读出谐振器耦合器)。d的值通常在5微米和10微米之间,较小的间距会增加芯片间的电容(与平行板电容相比),从而增加耦合率,但会增加电场再分布(与平面设计相比),从而改变设备参数,例如传输线的相位速度。

二、设备架构和制造

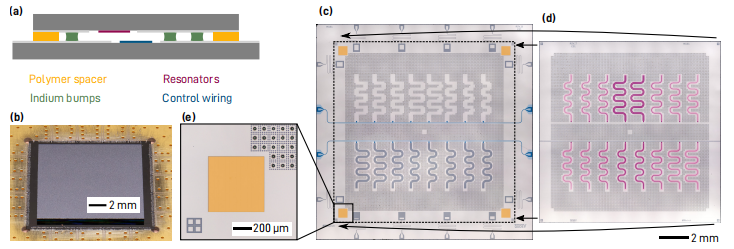

我们的多芯片模块[图1(a,b)]包括一个谐振器芯片(顶部)与一个线路芯片(底部)的粘合,其名义间距为10微米。在这里,线路芯片[图1(c)]包括复用馈线以及与分路印制电路板(PCB)的焊接连接,而所有谐振器都在顶部的谐振器芯片[图1(d)]上。超导金属铟凸块(直径25微米,厚度10微米)为谐振器芯片提供机械支撑,并将两芯片的接地平面电镀连接,以抑制杂散模式。底部线路芯片在重叠区域的角落中有600微米×600微米×10微米的SU-8光刻胶垫,在凸块粘合过程中支撑谐振器芯片,并作为机械止动器确保均匀的芯片间距[图1(e)]。光学显微照片的大图见附录B。

图1 所提出的三维集成方案的概述。(a)我们的倒装芯片键合结构示意图,包括聚合物间隔物(不按比例排列)。(b)一个倒装芯片连接的模块有线连接到PCB的照片。(c)底部布线芯片和(d)顶部谐振器芯片的彩色光学显微照片,具有馈线(蓝色)、谐振器(红色)和SU-8间隔片(黄色)。(e)SU-8间隔层的细节也显示铟凸起(绿色)。

三、SU-8垫片性能

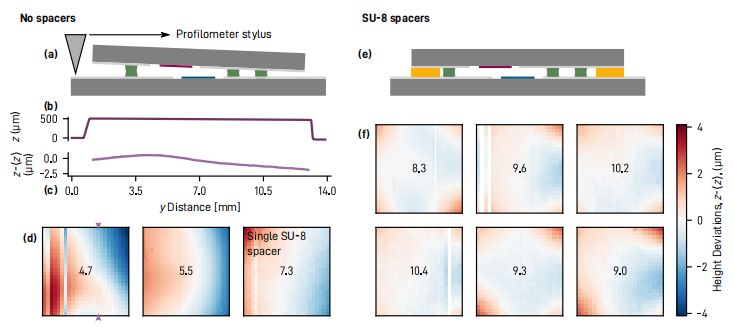

为了全面检查芯片间的间距,我们使用机械轮廓测量法,如[图2(a)]所示,一个测针在样品上直线移动,同时记录偏移量,从而得到高度与位置的线扫描图[图2(b)]。我们观察到从底部芯片的上方表面到顶部芯片的上方表面的一个步长,刚刚大于500微米,这对应于顶部芯片的基板厚度加上芯片间距。我们根据底部芯片对数据进行校平,并窗口化顶部芯片区域,得到一个轨迹[图2(c)],其轮廓平滑变化,有一些倾斜和弓形(曲率),并且总偏差约为3微米。

图2 机械轮廓测量法测量。(a) 无间隔的倒装芯片键合器件的示意图,说明了机械轮廓测量仪探针的扫描方向。(b) 原始轮廓数据和(c)经过校平、裁剪到顶部芯片区域并减去整个顶部芯片区域的平均高度后的数据。(d) 无间隔的模块的机械轮廓测量仪高度图。最左边的面板中的紫色箭头指示了(c)中给出的轨迹。最右边的面板在左上角有一个单个间隔,如所示。(e) 有间隔的倒装芯片键合器件的示意图和相应的高度图(f)。高度图的大小约为11毫米×11毫米。颜色表示每个模块相对于平均顶部芯片高度的偏差,而每个子面板中心的数字是提取的平均芯片间距(测量值减去估计的顶部芯片基板厚度)。

进行一系列这样的线扫描,并按照上述方法处理数据,我们准备了图2(d,f)中的高度图。由于轮廓测量仪中的测量误差,高度图中的一些线扫描与相邻的线扫描相比偏移了几微米;我们删除了(屏蔽)这些轨迹,结果在图2(f)中产生了白色的垂直线。请注意,在绘制图2(c,d,f)中的数据时,我们从显示的数据中减去了整个顶部芯片区域的平均高度。此外,我们指出,该技术无法区分芯片间距与顶部芯片基板的厚度变化。此外,我们测量了我们晶片厚度的标准偏差(在1.0微米或以下),这一点在附录C中进一步讨论。

在没有间隔的器件中[图2(d)],我们观察到大的倾斜,这由颜色梯度和相对于平均值的±4微米的偏差证明。一旦加入间隔物[图2(f)],倾斜就会大大减少,并且样品的一侧到另一侧不再有大的芯片分离梯度。相反,现在避免了大的倾斜,我们观察到弓形,角落被抬高了大约1微米,而中心被压低了略少于1微米。

图2(d,f)),我们减去估计的顶部芯片基板厚度(来自独立测量值;见附录C)。我们观察到4个没有间隔的器件平均分离(5.8±1.9)µm,9个有间隔的器件(9.6 ± 0.8)µm。我们通过最小二乘方法拟合数据平面来计算这些芯片的倾斜,得到无间隔器件的平均倾斜为(269 ± 151)µrad,有间隔器件的平均倾斜为(76±35)µrad。因此,根据我们的分析,间隔层将目标分离的误差减少了10倍,倾斜度减少了3.5倍。

四、结论

为了提高铟倒装芯片键合超导微波电路的参数可重复性,我们开发了一种SU-8间隔物工艺。我们发现,间隔物将平均芯片分离误差和倾斜度分别降低了10倍(平均为(0.4±0.8)微米)和3.5倍(平均为(76±35)弧度)。此外,我们证明了轮廓测量技术能够通过揭示在芯片角落的SEM测量或预键合间隔物高度测量中不可见的弓形来表征整个键合区域。需要对这种弓形进行进一步研究,特别是添加额外间隔物的影响。SU-8间隔物由于其制造过程的简单性和可及性而具有优势。根据我们的测量,SU-8间隔物与硅和铟间隔物的性能相当。然而,为了评估其与量子比特的兼容性以及最佳方法,特别是考虑到其在标准清洁步骤中易吸收溶剂的倾向,需要进一步研究。

对谐振器品质因数的测量表明,倒装芯片键合工艺在质量因子为5×105的水平上保持了类似平面制造工艺的低损耗材料界面。具有更宽中心导体的谐振器达到了更高的内部品质因数,以换取对芯片分离偏差的潜在增加敏感性。我们没有发现金属面和介质面谐振器之间的显著差异,这表明我们可以根据设计方便性使用它们。特别是,由于它们对芯片间距偏差的相位速度敏感性降低,介质面谐振器可能以物理上更长的谐振器为代价而更受欢迎,因为它们的相位速度较低。需要更多的工作来研究替代几何形状(微带状),以避免窄CPW线路的质量因子惩罚,并保持与分离无关的属性。

下一篇: 旋涂法沉积氧化铝薄膜用于硅片表面钝化