摘要

我们对III-V/si基混合波导系统进行了全面的数值研究,作为集成的III-V量子点发射器与集成在硅衬底上的片上量子光子集成电路之间的有效光耦合平台。我们提出了一个由一个混合的InP/Si波导和一个嵌入的InAs量子点组成的平台,在近1550 nm处的电信c波段发射。该平台可以使用现有的半导体处理技术来制造。我们的数值研究表明,考虑到沿锥形几何形状的传播场,几何优化的InP/Si和Si波导之间的光场传输效率为近87%。定向偶极子发射对混合InP/Si波导的耦合效率的∼为38%,这导致了从偶极子到Si波导的总片上光场传输效率的33%以上。通过研究芯片平面的法向和平面内的外耦合结构,考虑了沿传播光子场在硅波导上的片外外耦合效率。

一、介绍

这些电路基于光子的量子特性进行设计,可用于量子信息处理和计算、量子通信以及量子测量等新兴领域。和传统的光子集成电路(PICs)一样,芯片规模的集成是一个关键因素,能够提供小型化,从而减小系统占用的空间,提高可扩展性,增强机械稳定性,降低能源和材料消耗,并降低制造成本。为了实现全面的应用能力,qPIC需要在一个单一的晶片级平台上集成各种被动和主动的光学元件,包括非经典光生成、光子路由、控制整个qPIC元素,以及在单光子水平上的检测。此外,还需要将光子输出到外部光子环境。目前,许多现有的材料方法正在被考虑用于开发真正功能性的qPIC,包括硅基底上的二氧化硅(SOI)、硅氮化硅(Si3N4)、硅氧化氮、铝氮化物(AlN)、碳化硅(SiC)、锂酸铌(LN)、钻石(C)、聚合物、钽五氧化物(Ta2O5)、镓砷化物(GaAs)和磷化铟(InP)等。然而,在所有这些材料中,实现功能性qPIC设备的单片集成仍然非常具有挑战性或不可能,因此需要将不同的材料混合在一起。

硅基底上的二氧化硅(SOI)作为量子光子集成电路(qPICs)集成的主要材料平台的吸引力。SOI平台已被成功用于传统的光子集成电路,具有与成熟的互补金属氧化物半导体(CMOS)技术兼容等优点,从而可以对qPICs元件进行电子控制。此外,SOI平台提供了高指数对比度,对于光子路由是必要的,并确保了低成本、成熟和高加工产量。在Si平台上,可以制造各种单片组件,包括分束器、交叉器、相位调制器、滤波器、电光开关、波导、多路复用器、微环谐振器以及光子探测器。值得注意的是,硅平台为芯片内的光子路由提供了超低的损耗,由高折射率支持。对于量子光电器件的扩展性,芯片内的低光子损耗是首要因素,也是扩展性的限制因素。然而,主要的障碍是缺乏兼容的非经典光子源。和其他材料平台一样,将非经典光子发生器与Si平台相结合似乎是一个具有挑战性但必要的解决方案。

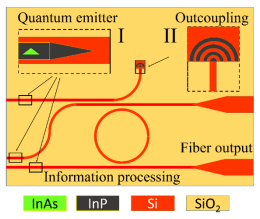

我们研究了锥形混合InP/Si WG部分的传输特性。我们的目标是提供最高的耦合效率,将InAs/InP QD限制的偶极发射与Si WG耦合,通过锥形几何形状实现最大的光传输。我们通过扫描锥形几何形状的扩展参数空间,然后模拟多个锥形结构的多模传播来实现这一点。接下来,我们评估了一个偶极、定向发射耦合到一个特定的混合InP/Si WG中的导模,使用中心偶极位置,并随着横截面位移的变化而变化。最后,我们研究了从Si WG到自由空间的发射耦合的可能性,这模拟了qPIC与外部传输通道(例如光纤)之间的联系。我们检查了每个组件的传输/耦合效率相对于传输光子波长的范围为1.5-1.6µm,这对于与组件制造过程的不完善相关的设备容差非常重要。所有在芯片上通信的组件可以组成一个设想中的用于量子信息处理的纳米光子电路,如图1所示。

图1 利用在普通SOI平台上嵌入在混合InP/Ii波导中的InAs/InP量子点发射器进行量子信息处理的纳米光子电路的概念。一个典型的纳米光子芯片可能由光子源、耦合器、分裂器、环形谐振器和从PIC到芯片的平面内或平面外方向的光外耦合系统组成

二、方法和模型结构

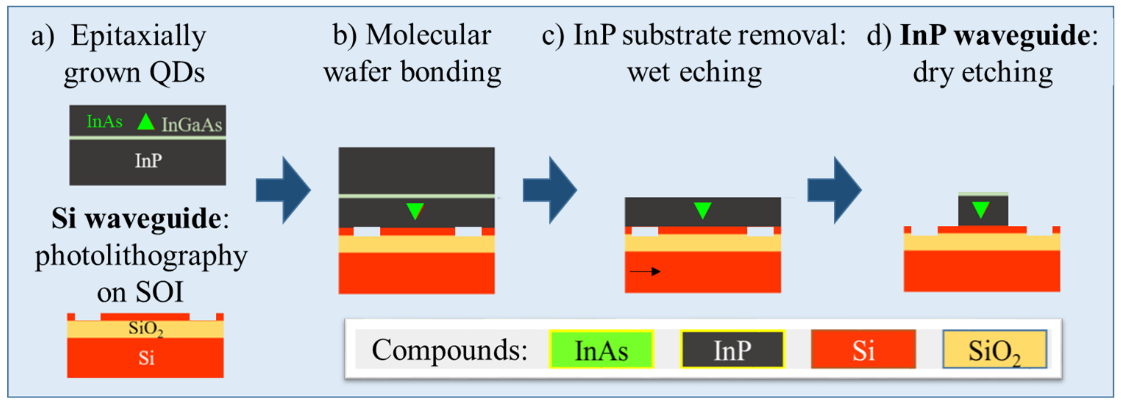

InP和Si波导以及混合波导的几何形状在Lumerical 3D CAD环境中的建模。虽然模型是概念性的,但主要关注的是找到一个与成熟的制造和加工步骤一致的现实模型。实现这些结构有几种可能的方法,包括(i)原位光刻,(ii)转移打印,或(iii)拾取和放置方法。对于每一种技术,至少可以确定一个挑战:(i)需要的设备复杂,(ii)制造精度低,(iii)工艺成品率低。另一方面,直接晶圆键合后电子束光刻(EBL)已成功应用于制造GaAs/Si3N4波导[24]。键合方法的优点是相对较低的复杂性,导致更好的可扩展性和高制造精度(<50纳米,相比之下转移打印的精度为约1微米)。值得注意的是,所呈现的几何优化结果与制造方法无关,但为了证明我们方法的实用性,我们给出了基于直接晶圆键合的详细制造过程。这需要将包含自组装InAs量子点的InP晶圆与SOI晶圆集成,然后进行WG加工。加工过程将从在SOI晶圆顶层刻制Si波导和校准标记开始。下一步是使用等离子体激活的直接键合将InP与图案化的SOI芯片粘合,然后去除InP基底。然后,将先前在Si层中定义的未遮盖的校准标记用作确定性的InP WG模式定位的参考(在Si WG上)。最后,通过干蚀刻将混合波导的最终模式转移到InP层中(使用基于干涉测量的计量学来控制蚀刻速率或薄氧化层的沉积作为蚀刻停止)。制作步骤的概述如图2所示。

图2 所提出的制造工作流程,以实现在硅绝缘体(SOI)平台上的异质集成InAs/InP量子点系统的量子光子集成电路:a) 准备带有量子点的InP晶圆和带有定义Si波导的SOI晶圆,b) 分子晶圆键合工艺,翻转InP晶圆,c) 湿化学刻蚀工艺,去除InP基底,d) 干刻蚀工艺,在Si波导上定义InP波导。

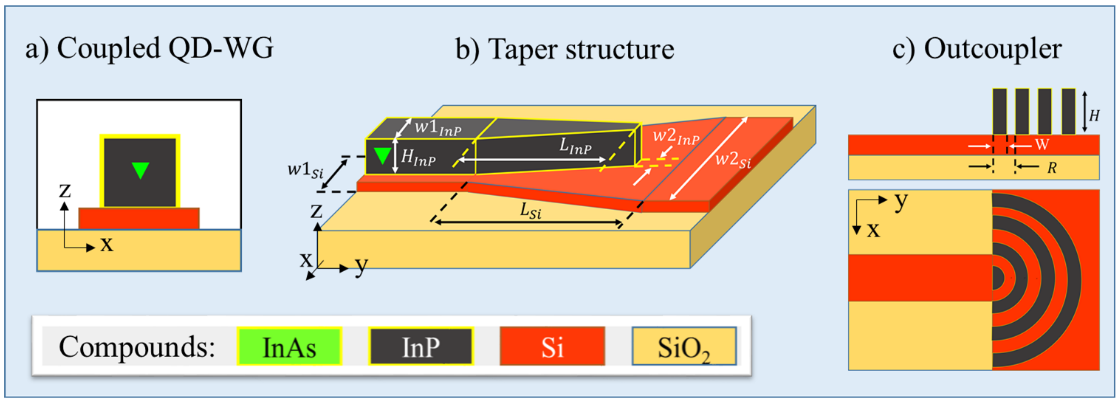

实现InP部分对基模的限制,混合InP/Si波导几何形状的主要要求是Si部分必须比InP部分窄。然而,我们预计该结构在机械上是不稳定的,因此我们的概念设计中的后续结果考虑了相反的约束,即较窄和较高的InP部分位于较宽和较薄的Si部分之上。所提出的制造方法可以用于实现图3所示的混合InP/Si波导。它由三个元件组成,可用于开发一个简单的qPIC演示器,在单光子水平上使用嵌入式InAs/InP量子发射器。第一个元件是包含有单个InAs QD嵌入的InP波导的混合波导结构,第二个元件是锥形结构,其中InP和Si波导都具有锥形几何形状。对于InP波导,锥形沿着模态传播方向收缩,而对于Si波导,使用倒锥形几何形状。在这里,我们只考虑锥形长度等于或小于Si波导锥形长度的情况。两个锥形在波导方向上具有线性宽度依赖性。第三个元件是Si波导部分,它是Si波导锥形端部的延伸,没有顶部InP波导。此组件由出耦合环结构终止,可用于将转移的光散射到垂直于结构平面的芯片外检测系统。在两种情况下,都可以使用显微镜物镜或带透镜的光纤来实现光子出耦合,以实现高收集效率。

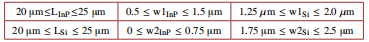

在耦合器部分(锥形区域)之后,被限制在Si WG中的光被收集在结构的最后一个部分的末端(SiWG的末端)。因此,各自的光透射可以计算为T=PSiWG/Psoucce,其中PSi WG是在Si WG末端收集的光功率,P源是注入混合InP/Si WG的光功率。根据所提出的混合WG的几何形状(见图3),我们通过检查以下混合WG参数的空间来评估光传输效率: LInP、LSi、w1InP、w2InP、w1Si w2Si。这些参数根据图3(b)分配,其范围如表1所示:

表1

图3 综合量子光子电路的元件,具有在混合InP-Si波导系统中集成的量子点:a)波导中的量子点耦合,b)线性锥形结构,c)光栅出耦合器。所有这些元件都可以通过使用图2中提出的制造方法来实现。

三、结果

从InP到Si波导的光传输

我们研究了从混合波导部分传播的光场通过锥形区域到Si WG部分的传输效率。为了模拟嵌入InP WG中的单个InAs量子发射器生成的光场,我们使用高斯光束源(腰半径为0.50-0.55 µm,取决于w1InP)沿波导提供方向传播的光场。高斯光束沿波导的方向传播简化和推广了寻找高效锥形结构的问题。首先,该源激发了多模态传播,类似于随机的一组电偶极子,这与InAs层中自组装QD的平面内随机分布的预期位置不确定性以及QD层在生长过程中确定的垂直移动有关。其次,高斯光束源的方向性允许评估锥形传输效率T为半对称双向偶极子耦合。第三,由于折射率对比度的不优选顺序,即nInP < nSi,高斯光束位于InP中,避免了激发Si中的基模,有利于InP中嵌入的QD的相关高阶模式。在这种方法中,对于给定的锥形结构几何形状进行单次模拟可以提供可靠的结果,而不是使用耗时且资源消耗的单极子模型。然后,通过锥形几何形状的参数扫描,我们可以更有效地搜索优化系统,实现从混合WG到Si WG的光场传输的最大效率。

四、结论

在这项工作中,我们重点研究了在绝缘子上硅平台上开发的非均匀集成混合波导系统的数值研究,以证明其作为可扩展的量子片上光子集成电路的能力。该结构可以通过标准的光束或电子束光刻技术来制造,利用一个键合步骤来连接不同材料的两个晶片。其中一种材料可以基于III-V化合物,例如InP,它允许制造高质量的量子点发射器,使用,例如InAs,并在1550 nm光子波长工作。因此,我们研究了混合InP/Si波导中的偶极耦合,基于截面几何的模式结构,引导光从InP/Si混合系统有效转移到Si波导的线性锥度结构,以及可能的外耦合。首先,我们发现偶极子与InP/Si波导模的偶极子耦合率为38%。此外,在波导的一侧施加反射器或采用手性耦合效应可以保证单向性消除了精确控制量子点发射波长的问题,这是空腔制造过程的关键。最后,我们研究了基于圆形布拉格光栅的平面外采集系统和平面内采集的光点尺寸转换系统所实现的解耦合效率。结果表明,垂直外耦合效率为26%,平面内为10%,NA均为0.65,均显示宽带可操作性。