在先进的工艺控制中,使用R2R控制已经很好地解决了批次与批次之间以及晶圆与晶圆之间的工艺差异,然而,为了解决在65纳米技术节点及以后不断增加的管芯与管芯之间(即跨晶圆)的工艺差异,工艺控制必须扩展到更精细的领域:跨晶圆级。

提出了一种新的基于模型的工艺控制方法[2],以减少整个晶片水平上的临界尺寸(CD)变化。所提出的方法的中心思想是通过调整多区烘烤板的跨晶片曝光后烘烤(PEB)温度分布来补偿上游和下游系统CD变化。使用来自的无线温度传感器实验性地构建了将多区域烘烤板的PEB温度分布与其加热器区域偏移相关联的温度-偏移模型。提取基线蚀刻后CD特征和等离子体蚀刻偏置特征来表征光刻和蚀刻工艺。并且在验证实验中实现了40%的蚀刻后CD变化减少,这验证了所提出的方法的有效性。

关键词

R2R控制、先进工艺控制、临界尺寸均匀性(CDU)、临界尺寸变化、PEB温度、多区域烘烤板、等离子体蚀刻偏差信号

介绍

随着晶体管几何尺寸的缩小和晶片尺寸的增加,跨晶片工艺变化,特别是CD变化已经变得越来越重要。在亚0.1 mm范围内,栅极临界尺寸(CD)的控制至关重要,并且跨晶片CD变化的限制变得更加严格。就时钟速度和功率而言,跨晶片栅极临界尺寸的均匀性影响最终芯片到芯片的性能可变性。根据ITRS 2005,对于65纳米技术节点,栅极CD必须控制在2.6纳米(3σ),这是一个性能目标,目前还没有可制造的解决方案。为了很好地解决跨晶片级CD变化,先进的工艺控制必须将其控制范围从批次到批次和晶片到晶片扩展到跨晶片级。

多种因素导致光刻和蚀刻顺序中的跨晶片CD变化。这些包括涂覆、烘烤[1,2,3,7]、曝光、显影和蚀刻步骤中的不均匀性。很明显,减少跨晶片CD变化的最简单和最直接的方法是使每个单独的处理步骤在空间上均匀。不幸的是,这对于300毫米晶片加工来说过于昂贵。此外,并不是通过光刻和蚀刻顺序的每个处理步骤都提供空间控制权限。具体而言,在典型的蚀刻工艺中,空间可控性受到严重限制。唯一潜在可用的控制机制是双区ESC冷却系统中背面氦气压力的调节。然而,由于其仅有的双区配置,背面氦气压力调节在蚀刻过程中提供非常有限的空间控制权限。光刻步骤提供了更多的空间控制机会。这包括逐个芯片的曝光通过调整加热器区域控制器的偏移和PID设置[2,7],对PEB步骤中的空间温度曲线进行剂量调整[4]。这两个控制输入通常很容易接近。然而,当在光刻轨道簇中使用多个烘烤板时,可变曝光剂量的使用不是最佳的。这是因为烘烤盘在温度和排气曲线方面通常是不同的,并且这两个属性的完美匹配是不可行的。因此,这项工作的中心思想是放弃曝光剂量控制,并有意地去调谐使用中的每个板的跨晶片PEB温度分布。这将通过补偿诸如薄膜和显影不均匀性、烘烤板排气信号和等离子体蚀刻偏置信号等其他系统变化源来提高整个晶片的蚀刻后CD均匀性。

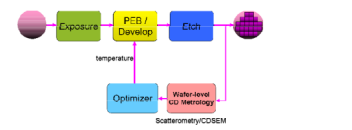

图1示出了提出的CD均匀性控制方法。如果可以通过调节多区烘烤板的AW PEB温度空间分布来平衡整个AW CD变化源,则可以最小化跨晶片(AW)蚀刻后CD变化。这是可能的,因为本地PEB温度直接控制本地CD。

II.PEB温度到区域偏移模型和CD到区域偏移模型

这是温度与失调模型,其中Oj是区域j的控制器失调,Ti是传感器晶圆[5,6]上的传感器I测得的温度,该晶圆表面分布有m个传感器。该温度是烘烤盘的7个区域控制器偏移的函数,因为由于烘烤盘良好的导热性,每个区域控制器偏移都会影响整个烘烤盘的PEB温度。一般来说,钛(O1,氧气...O7 )是一个非线性函数,但是当烘烤盘被很好地校准时,使用线性模型来近似它是有效的。每个温度传感器的局部线性模型可以在设计的实验中从PEB温度测量值实验性地构建。AW PEB温度与测量的基线PEB温度的偏差可以表示为:

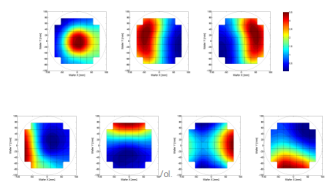

等式(2)中的矩阵G通过线性回归获得,并且它是温度-偏移模型的核心。其第j列表示第j区控制器偏移对AW稳态PEB温度的影响。设计并实施了8轮27-4部分因子实验设计(DOE)来提取温度-偏移模型。图2.a和2.b描述了每个区域控制器偏移对相应区域偏移1个单位增量的AW稳态PEB温度的影响。它们清楚地表明每个区域控制器偏移有效地控制了晶片特定区域上的PEB温度。此外,区域控制器偏移的影响随着远离区域中心而逐渐减小,并且晶片温度随着区域控制器偏移的增加而降低。

图3:从温度-偏移模型导出的CD-偏移模型和以nm为单位的抗蚀剂PEB灵敏度。

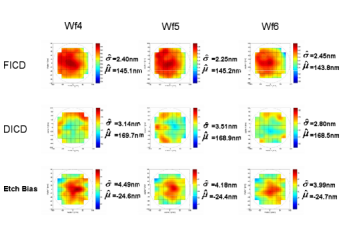

图6:第3周在PEB板A上烘烤的晶片的FICD、DICD和蚀刻偏差

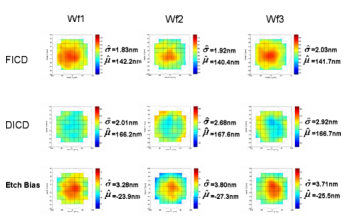

图7:第一周在PEB板B上烘烤的晶片的FICD、DICD和蚀刻偏差

使用两周平均基线FICD和蚀刻偏差特征以及提取的抗蚀剂PEB灵敏度,使用所提出的方法计算最佳区域控制器偏移调整,并对验证晶片进行构图,以验证所提出的蚀刻后CDU控制方法的功效。图11显示了晶片1和晶片2的基线FICD、预测的(通过模型)最佳FICD和测量的最佳FICD,以及晶片1和晶片2的预测的和测量的最佳FICD之间的差异。我们可以看到,在表征实验中,测得的最佳FICD的变化比基线FICD小约1nm,并且大于预测的最佳FICD。这是由于模型缺陷和计量噪声的结合。考虑到在表征实验和FI CDU控制验证实验之间已经过去了6个多月,所实现的FI CDU改进确实是有希望的。如果可以利用集成计量来缩短基线表征和PEB偏移调整之间的时间延迟,则可以实现额外的CDU改进。图12可视化了模型预测的跨晶片PEB变化、测量的跨晶片PEB变化以及预测的和测量的跨晶片PEB变化之间的差异。我们观察到,当本地基线FICD较大时,管制员如预期的那样,提高了本地PEB温度,以降低FICD。图13中示出了等离子体蚀刻偏置信号和理想的DICD图,该图将完美地平坦化所得到的FICD。图14显示了模型预测的DICD、测量的DICD以及它们之间的差异。我们可以清楚地看到,预测的和测量的DICD都试图形成相反的等离子体蚀刻偏置的空间特征,使得最终的FICD均匀性将被优化。模型预测的DICD和测量的DICD之间的差异可能是由模型缺陷和计量噪声引起的。从测量的FICD和DICD特征提取最终的蚀刻偏置特征,如图15所示。这表明等离子体蚀刻偏置信号是稳定的,并且其空间特征在6个月期间没有显著变化。这验证了我们选择将偏差信号视为固定的、可观察的、但不可控制的干扰的合法性。

在采取控制措施后,DICD变化变得更糟,因为它试图形成下游等离子体蚀刻过程的相反信号,从而可以消除下游等离子体蚀刻信号,以提高最终的FICD均匀性。

上一篇: 使用IPA溶液去除晶圆上静电荷

下一篇: 硝酸浓度对硅晶片腐蚀速率的影响