In a typical chemical-mechanical polishing (CMP) process for interlevel dielectric planarization, the oxide removal rate is strongly dependent on the parameters such as applied load, relative speed, and pad surface properties. However, the experimental results presented in this work show that by maintaining a thin fluid film between the pad and the wafer and thereby reducing the role of the asperities in the pad, the oxide removal rate can be made independent of these polishing parameters. In this semidirect contact mode, the CMP process, carried out on 2 in. wafers, resulted in a uniform polish rate across the wafer, high run-to-run reproducibility, high selectivity between materials of differing chemical properties, and eliminated the need for pad surface conditioning and in situ end-point determination equipment.

Introduction Chemical-mechanical polishing (CMP) has been in use for optical finishing of glass and Si surfaces for many decades. I Application of CMP for the planarization of interlevel dielectric (silicon oxide) as well as for polysilicon and tungsten metal studs was pioneered by IBM and has been used in the fabrication of very large scale integrated (VLSI) circuits since 1985. 2.3 It has now emerged as the most effective method of achieving global planarization in multilevel circuits with feature sizes less than 0.5 ~m, in order to meet the shallow depth-of-focus requirements of optical projection lithography equipment. 4 Although this technology has been mainly developed for Si integrated circuit (IC) manufacturing, its use has now been extended to other thin film circuits where small feature sizes and multilayer interconnections are required. ~ CMP is carried out by pressing a rotating wafer against a moving polishing pad on which a suitable slurry is dispensed. For oxide polishing, the slurry consists of silica particles dispersed in an aqueous solution. The oxide surface is chemically modified, and this modified layer is removed by mechanical action. As the removal rate is a function of the height of a feature in relation to its surroundings, CMP reduces the surface topography, producing highly reflecting surfaces. This phenomenon is utilized in IC fabrication, where processing of multilayers produces surface irregularities such as steps at the edges of the layers and depressions where contact is made to an underlying layer. In spite of its heavy use in VLSI manufacturing, a limited information on the role of various CMP parameters such as pressure, relative velocity between the pad and the wafer, mechanical properties of the pad and the oxide, temperature, chemical reaction rate, and slurry flow distribution, is available in the open literature. Theoretical modeling of such a complex system has so far only been done based on simple mechanical models. 6'7 While altogether neglecting the chemical reactions in the process, the models do not even take into account the full range of mechanical and hydrodynamic parameters such as surface roughness of the pad, pad-wafer contact area, slurry flow pattern, and the residence time of slurry particles on the wafer. In general, CMP does not provide good selectivity between different materials, making it difficult to determine the end point in this "blind" experiment. A high run-to-run reproducibility and a uniform polish rate across the wafer are therefore very desirable for a timely termination of the process. Usually a trial and error method is adopted to obtain the most suitable polishing conditions for a specific application. In manufacturing, the process is qualified by employing statistical methods to determine the effect of process variables. These techniques require that a large number of experiments be conducted for each specific tool and application. The entire procedure is therefore time consuming and expensive but essential for a successful application of CMP. It is no surprise that, so far, only large organizations have been able to utilize this process to their advantage and most of the experimental details are proprietary. In this work, an empirical approach is adopted to demonstrate the solid-solid and solid-fluid interactions in CMP, as applied to interlevel dielectric planarization (ILD). This is accomplished by suitable modifications of the wafer mounting assembly, which changes the pad-wafer contact and the fluid flow distribution across the wafer. A brief theoretical background describing the existing models for CMP is given and the appropriate references cited. In the experimental data presented here, when the wafer is in partial contact with the pad, the oxide removal rate is found to be independent over a wide range of process parameters such as pressure, relative velocity, and pad surface properties. The experimental procedure for realizing these conditions may be dependent on the specific polishing equipment and wafer size. The main object of this work, however, is to demonstrate a robust CMP process, relying on the chemical reactivity of the oxide, for achieving a uniformly high removal rate across a wafer. In addition, this process provides effective planarization for ILD applications. The experiments reported here were carried out on 2 in. diam Si wafers with silicon oxide as the dielectric layer. A planarization process, similar to the multilevel metallization process used in VLSI fabrication, was developed for the fabrication of Nb-based superconducting circuits.

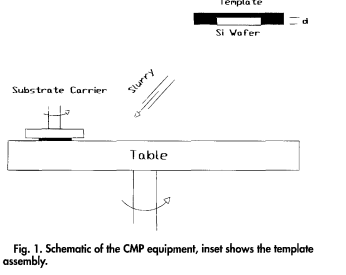

Experimental The wafers used in our experiments were 2 in. in diameter with thicknesses of 11 and 20 mils. Blanket (featureless) wafers were used for studying the dependence of oxide removal rates on the polishing parameters. The oxide films were either thermally grown quartz (SiQ) or thermally evaporated SiO. The two oxides have different chemical properties, SiO being more chemically reactive than SiO2. The refractive indexes of the SiQ and SiO are 1.46 and 2.0, respectively. CMP was carried out on a Model 6CA Strausbaugh polisher. A scheme illustrating the essential features of this single-wafer CMP equipment is shown in Fig. 1. The wafer carrier and the table rotational speeds are controlled independently, and a small lateral motion is provided to the substrate carrier to reduce pad wearing. The wafer carrier and the water-cooled table on which the polishing pad are mounted are both rotated in the same direction to maintain a constant relative velocity at all points of the wafer. TM The wafer is mounted on a template assembly for a single 2 in.

上一篇: 用于晶片到晶片堆叠的硅减薄工艺的表征

下一篇: 表面粗糙度对晶圆直接键合的影响