Abstract: Low-temperature direct Plasma-Enhanced Chemical Vapor Deposition (PECVD) oxide to thermal oxide bonding is described. The PECVD oxide is densified at 350o C and chemical-mechanically polished to obtain reasonably smooth surface for bonding. The PECVD oxide wafer is bonded to the thermal oxide wafer at room temperature after piranha clean that leaves the wafer surfaces hydrophilic. A postbonding anneal at 300o C completes the bonding. A void-free bonding interface is observed from infrared imaging and the bonding strength is estimated to be 432 mJ/m2 . This bonding method can be used in a variety of applications, including threedimensional integration.

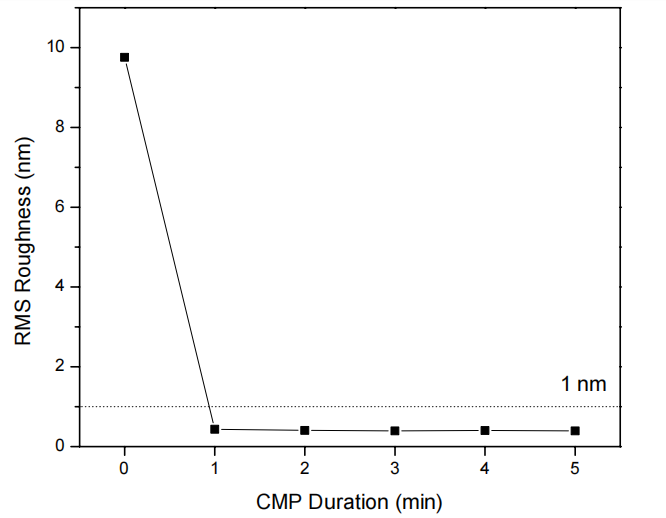

Three-dimensional (3-D) integration, in the form of a vertical stack of several device (with interconnect) layers, has many potential advantages over conventional horizontal planar integration [1]. There are research efforts on developing possible technology options to realize a 3-D structure, either using recrystallization [2,3] or wafer bonding [4,5]. We have recently proposed a 3-D integration method using direct Cu-toCu wafer bonding [6]. In this scheme, a thinned silicon-on-insulator (SOI) device layer is bonded to a substrate device wafer in a back-to-face fashion. This requires bonding of the SOI wafer to a handle wafer followed by SOI wafer etchback. The thinned SOI layer is then bonded to the substrate device wafer using Cu as the bonding medium. Note that the bonding between the SOI wafer and the handle wafer is a sacrificial one, as the handle wafer will be released at the end of the process. Hence, this bond has to be strong enough to hold the SOI wafers during subsequent processes. However, the same bonding should release readily during SOI thin-film transfer onto the substrate wafer. Epoxy [7] and adhesive [8] have been investigated, but they are not compatible with the process temperature during Cu wafer bonding at 400o C and the chemical attack during SOI wafer etchback. In this letter, we describe a direct thermal oxide to Plasma-Enhanced Chemical Vapor Deposition (PECVD) oxide wafer bonding for this application. The choice of two different oxides will be explained below.All wafers used in our experiment were p-type 4” Si(100) wafers of 10-20 Ω-cm resistivity. Two sets of wafers were prepared: One was the handle wafers and the other was the dummy SOI wafers. The handle wafers were covered with 5000Å of thermal oxide for protection against chemical attack during SOI wafers etchback. Wet silicon etchants such as KOH and TMAH are known to have excellent selectivity towards thermal oxide [9]. Dummy SOI structures were prepared by growing 5000Å of thermal oxide as buried oxide (BOX) followed by a deposition of 4000 Å undoped polysilicon at 620o C. The SOI wafers were then coated with 4µm of silane-based PECVD oxide at 400o C. In actual device wafers with metal interconnects, PECVD oxide is an attractive choice as interlayer dielectric (ILD) because of its high deposition rate and its low temperature process. However, due to the non-equilibrium nature of the PECVD process, byproducts or gas molecules may be incorporated into the deposited film and result in out-gassing during subsequent processing [10]. To prevent undesired out-gassing from the PECVD oxide film during subsequent heat treatment of the bonded wafer pairs, the SOI wafers were densified in atmospheric N2 ambient at 350 o C for 16 hours. Since as-deposited PECVD oxide exhibits a relatively high surface roughness, direct bonding using such wafers are often unsuccessful. Therefore, the SOI wafers were chemical-mechanically polished after densification to increase both the surface smoothness and the bonding yield. To ensure that this bonding method is useful in real device wafers, a low temperature process is essential to avoid undesired thermal damage. Hence, a hydrophilic bonding was chosen. All wafers received a 10 min piranha (H2O2 : H2SO4 = 1:3) solution clean followed by deionized water rinse and spin-dry. This cleaning was necessary to clean the polished wafers and to terminate the wafer surfaces with hydroxyl (OH) groups to initiate wafer bonding. Handle wafers were aligned to SOI wafers in an EV1 aligner and the pairs were subsequently transferred to a bonder. The chamber was purged with nitrogen and evacuated to 10-3 Torr. Bonding occurred at room temperature under a pressure of 1000 mbar for 5 min. Figure 1 is a schematic showing 4 the bonding process. After bonding, the wafer pairs were annealed at 200 o C and 300 o C respectively for 6 hours in atmospheric N2 ambient to enhance the bonding strength. To achieve high quality bonding, the root-mean-square (RMS) roughness of the wafers must be below 1.0 nm [11]. Atomic force microscopy (AFM) is a powerful tool to scan the surface profile and to measure the roughness of different materials. We have performed AFM surface scans on various wafers in the tapping mode on a D3000 unit from Digital Instruments. Table I summarizes the mean and RMS roughness of various wafers with different surface preparations. The handle wafers with a layer of 5000 Å of thermal oxide exhibit an RMS roughness of 0.273 nm, and this value is acceptable for bonding. Hence the handle wafers do not require additional surface polishing. On the other hand, the RMS roughness of the as-deposited PECVD oxide on SOI dummy wafers is 9.757 nm. This value is too high for wafer bonding and the wafers need extra polishing to smoothen their surfaces. We have also monitored the change in the surface roughness of the PECVD oxide as a result of densification. It was observed that densification has improved the roughness to 8.501 nm. This suggests that densification anneal has effectively improved the structure of the PECVD oxide. Figure 2 shows the RMS roughness of the PECVD oxide as function of chemical-mechanical polishing (CMP) duration. Note that CMP has improved the surface roughness tremendously to a value below 1.0 nm after one minute of polishing and the roughness does not improve significantly beyond one minute. Specifically, a 3 min CMP results in a roughness of 0.394 nm. In the bonding experiment, we have used 3 min of CMP on all PECVD oxide wafers unless otherwise specified.

Figure 2 Tan et. al., Applied Physics Letters

下一篇: 交叉污染对CMP后清洗过程的影响