INTRODUCTION

Pre-gate cleaning is unanimously considered as one of the key parameters governing thin gate oxide integrity and hence final device performance and yield. However, despite increasingly stringent process demands (cf. SIA road map), the basic cleaning recipe has remained almost unchanged since 1965. The RCA clean [1], in its multiple forms, is still the choice of preference for FEOL cleaning sequences in IC manufacturing around the world. The reason is simple: concentrated NH4OH/ H2O2/ H2O mixture (SC1) performs very well for particle removal, and so does the HCl/ H2O2/ H2O mixture (SC2) for metallic contaminants.

Recently cost-effectiveness and environmental concerns pushed considerable research efforts to optimize the RCA sequence and to develop alternative cleaning techniques. The first approach consists of diluting the SC1 and SC2 solutions, thus enabling important chemical savings at the same overall performances of the process. But implementation of diluted chemistries is not straightforward and there are many pitfalls to be avoided. Even then, some of the intrinsic limitations of the conventional RCA still remain valid for dRCA: high process temperatures (which is responsible for the major part of chemical consumption by evaporation) and multiple process steps. The use of diluted chemicals at room temperature represents another approach. The main new technological concepts have been introduced by IMEC [2], LETI [3] and professor Ohmi [4]. They all rely on HF-Ozone chemistry and include several sequences of ozonated water rinse(s) and dilute HF treatment(s). Basically the first Ozone step removes organics, noble metals, and oxidizes the wafer surface. The subsequent HF step removes the oxide as well as any embedded particles and metals. An additional ozone step is usually implemented to convert the hydrophobic surface to a more stable hydrophilic one. The reluctance of IC industry to adopt these relatively new cleaning strategies (even if very good performances have been extensively reported) suggests that an alternative intermediate approach is needed.

In this paper, a dilute RCA is proposed and the implementation of it in the wet bench is discussed. We present the latest technical advances in DDC. We also introduce a new Advanced Front End of the Line Cleaning, AFEOL, which consists of a combination of an HF-Ozone and a dilute SC1 chemistry (one could call this an intermediate approach between the dRCA and the DDC process). The exact process sequences are detailed in Table I. The cleaning robustness of these different advanced pre-gate cleanings is extensively analyzed and discussed.

Particle contamination removal

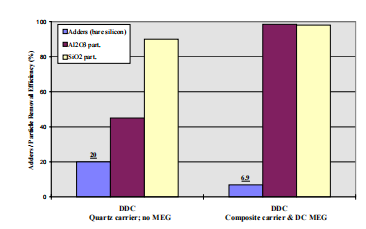

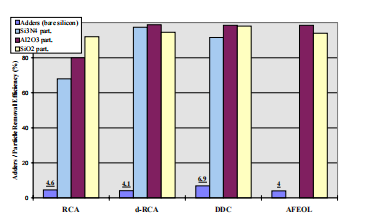

We investigated both the particle addition on clean bare silicon wafers (initial count < 10 Lpds @ 0,16µm) and the PRE of different particle types.

As can be observed from fig. 1B, this optimized dilute SC1 (used both in dRCA and AFEOL sequences) outperforms the conventional concentrated SC1 step. This, on first sight, strange behaviour is explained by the fact that the propagation of megasonic energy is enhanced at higher chemical dilution ratios due to lower gas bubble formation [6].

Fig1

Recently, the understanding of the fundamental of particle// substrate interactions has progressed significantly (influence of ionic strength, Zeta potential, temperature, megasonic, dissolved gas, … [8]). Taking into account these parameters in the advanced cleanings cycles will be crucial for future developments. On the other hand, diluting the SC1 even more immediately raises some critical issues for chemical concentration control systems and megasonic technology (frequency, power) [6].

Silicon Surface Roughness

To which extent Si surface roughness affects the gate-oxide integrity is still a controversial issue. Indeed when “unrealistic roughening” of the silicon surface is obtained (either by long treatment in BHF [12], or in hot DI water [13] or in alkali solution [14]), a yield loss is detected. On the other hand, the correlation between rms roughness and intrinsic oxide performances is not so clear when relatively smooth surfaces (low rms roughness) are involved [10]. This is actually the case since the rms roughness values we measured were between 0.9 to 1.3Å for RCA, dRCA or DDC clean and slightly higher for AFEOL ~2Å (HF RCA sequence also leads to ~2Å).

However what can drastically affect the intrinsic properties of gate oxide structures is the presence of high peaks on the silicon surface [15]. Therefore the ability of a cleaning process to smoothen an artificially roughened surface is very important. As is shown in Fig. 2, the DDC process is very effective from this point of view. The AFEOL cleaning is able to reduce the number of high peaks as well, but this is not the case for RCA nor dRCA process.

上一篇: 晶圆干燥的基本原理和技术

下一篇: 碳化硅和二氧化硅之间稳定性的刻蚀选择性