Abstract—Intimate integration of photonics with electronics is regarded as the key to further improvement in bandwidth, speed and energy efficiency of information transport systems. Here, a method based on wafer-scale polymer bonding is reviewed which is compatible with foundry-sourced high-performance InP photonics and BiCMOS electronics. We address challenges with respect to circuit architecture, co-simulation framework and interconnect technology and introduce our approach that can lead to broadband high-density interconnects between photonics and electronics. Recent proof-of-concept work utilizing DC-coupled driver connections to modulators, which significantly reduces the interconnect complexity, is summarized. Furthermore, cosimulation concepts based on equivalent circuit models are discussed with emphasis on the importance of impedance matching between driver and modulator. Finally, realizations of broadband interconnects and functional photonic building blocks after wafer bonding are highlighted to demonstrate the potential of this wafer-scale co-integration method.

THE motivation to integrate photonic functionality with electronic circuits has been long-lasting. Electronic Integrated Circuits (EIC) followed Moore’s Law scaling to reach today’s state-of-the-art billion transistor chips, capable of Teraflops of data processing . Photonic Integrated Circuits (PIC) are undergoing a similar progression, driven by the exponential increase in capacity demand of information transport systems, reaching thousands of components and terabit/s on chip . In both cases continued advances in the level of integration and the laws of scaling have been fundamental in meeting the communication and processing needs of today’s applications.

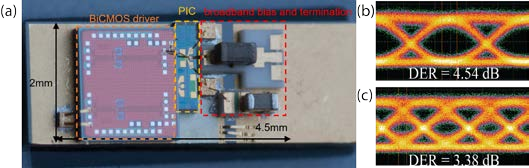

Conventional co-packaging concepts connect highly integrated electronics with densely packed photonics using wire bonds that run along the edge of the circuits . These introduce significant parasitics, causing signal degradations and, more profoundly, only allow a limited number of connections due to the one-dimensional nature of the interface. Stud bump bonding used in flip-chip assemblies supports broadband connections and provides a two-dimensional interface . This has been applied on die level and used successfully to connect high-speed DACs and drivers to EAM arrays and to terminate MZMs with resistive load chips . However, wafer-level packaging is preferred in industry for scalability reasons, as it can enable lower production cost and higher yield . Die-to-wafer and wafer-to-wafer bonding are two promising approaches here. We pursued the latter for its potential to achieve higher throughput and the possibility to define interconnects between electronics and photonics lithographically at fine resolution, going beyond what current die-level processes can achieve in density and size.

Fig3

The single-ended DC coupling only makes use of half the available driver output swing voltage. In contrast, differential DC coupling can utilize the complete output swing with reduced common mode distortion and has been suggested in . We have previously reported a novel driver design, shown in Figure 3, which is based on differential DC coupling that utilizes an asymmetric load configuration to provide up to -2V of bias for EAMs . It can also operate in single-ended drive and allows for two EAMs to be connected with separate bias adjustments. It has been fabricated in the same commercial 0.25 µm SiGe:C BiCMOS foundry technology, exhibiting 51.5 GHz bandwidth, 2V p-p output swing and open electrical eye diagrams at 56 Gb/s PAM-4 (VEC of 10 dB), leading to 3.9 pJ/bit power consumption . Most recently we have assembled the drivers with EAM modulators using the cointegration technology presented in section IV. The validation experiments are presently in progress.

下一篇: 沉积温度对多晶硅特性影响的表征