Silicon etching is an essential process step for the fabrication of micro-electro-mechanical systems (MEMS). As we enter the on-chip integrated sensor era, the sensing elements are typically defined after circuit fabrication. This has benefits in permitting the use of a standard technology such as CMOS and also in minimising the wafer processing after fabricating the often fragile MEMS structures. Structure definition in silicon must be carried out by dry etching when profile anisotropy is required (independent of crystal orientation), particularly for high aspect ratios. Although a variety of plasma etch tools and dry etch approaches have been reported in the literature, none have been capable of meeting the majority of MEMS dry etching needs. This paper presents a novel anisotropic silicon etch process which overcomes the limitations of other techniques and is fast becoming recognised as an enabling technology for a wide range of applications in MEMS fabrication.

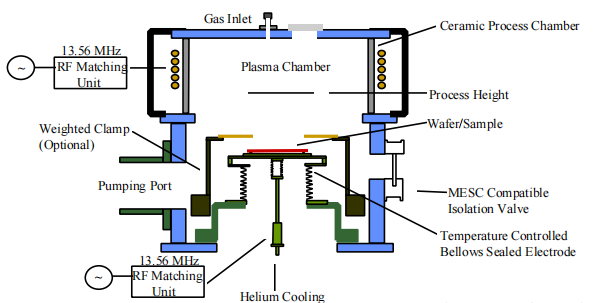

The precise requirements for the dry silicon etch process will determine the equipment suitability. For example, shallow, low aspect ratio etching can typically be achieved with standard capacitively coupled RIE etch equipment, although there may be some rate and mask selectivity advantages in using high density low pressure (HDLP) systems. However when it comes to shallow high aspect ratio etching or deep etching irrespective of aspect ratio, there is an increasing tendency to opt for HDLP plasma tools. The major benefit of operating in HDLP plasma mode is the reduction in ion collision probability as the sheath thickness decreases at higher ion density and the ion mean path increases at lower pressures1 . Improved ion directionality results and this in turn enhances the control of anisotropy. HDLP plasmas can be generated by a variety of excitation techniques, such as ECR, MORI, Helical Resonator, ICP, etc. Of these, the inductively coupled plasma source (whether helical or planar) offers the most stable and widest operating window. Hence the present work has been carried out in the STS-ICP system operating at 13.56 MHZ (excitation and bias frequency). Details of the plasma source technology and the STS ICP have already been presented elsewhere1 . A schematic of the STS ICP is shown in Figure 1.

Several approaches can be used to inhibit lateral etching during the process and thereby maximise the anisotropy. The most successful techniques are all based on sidewall passivation and this has been suitably covered in reference 1. Simultaneous etch and sidewall passivation processes have been successfully used in CMOS and in some limited (notably shallow etch) MEMS applications. A wide range of chemistries (such as HBr, Cl2/SiCl4 or SF6/O 2 etc.) allow suitable sidewall passivation to be formed during the etch. Here the passivation layer directly results from the chemical reaction between the dissociated precursor gas(es) and/or the silicon, possibly also with mask material contribution.

As a real potential solution for dry silicon etching for MEMS, considerable attention is now being paid to this new STS ASE process. This process is based on the technique invented by Lärmer and Schilp4 , and uses a variant of the sidewall passivation technique. Rather than the sidewall protection being an integral part of the process, here the passivation is deliberately segregated by using sequentially alternating etching and deposition steps. First a sidewall passivation polymer is deposited and subsequently the polymer and silicon are etched from the base of the trench, to allow the etching to proceed directionally. In this cyclic way the etching and deposition can be balanced to provide accurate control of the anisotropy.

Fig1

Plasma polymerisation reactions can be used to enhance the passivating layer, but in all cases relatively high ion bombardment energies (several hundred eV) are typically necessary to completely remove this layer from the base of the trench. In other words a strong physical component for the etch is necessary. Note, incomplete removal of this passivation component will result in the formation of grass-like residues and the appearance of “black silicon” as the inevitable rough surface results. This simultaneous sidewall passivation technique usually requires bi-level masking as photoresist masks can be inadequate in standing up to the physically aggressive nature of the process. Silicon dioxide or even metal masks are commonly used. Even so, etch selectivity to an oxide mask rarely exceeds 20:1 and etch rates range from several hundred nm/min up to 1µm/min. Chlorine and bromine based chemistries have provided some measure of success for high aspect ratios, albeit at shallow depths (<20µm) 2 . Clearly this limits the potential of this technique for MEMS applications.

Judicious chemistry selection is required to finely control this balance between the etching and the deposition. The deposited polymer must have good conformality, offer adequate sidewall passivation protection, whilst being readily removed by the etching plasma. Polymeric layers meet most of these needs5 , particularly since they need only low levels of surface ion bombardment in the presence of a reactive chemical in order to be completely removed from the surface. In this way, low self bias potentials allow the directionality of the etch to be easily controlled (which permits high selectivity to standard photoresists without compromising anisotropy). Etch precursor gases for this type of technique need to liberate high concentrations of chemical etchant to allow relatively high net processing rates taking the discrete deposition steps into account. Suitable candidates include NF3, SF6, etc. Polymeric deposition precursors may be based on a range of appropriate fluorocarbon chemistries such as CHF3, C2F6 and higher molecular weight gases with a higher C:F ratio.

Based on this segregated etch and deposition step technique, STS began an aggressive development program (in late 1993) for both the equipment and the process. This has culminated in today’s ASE process. The process chemistry adopted is non toxic and non corrosive and the wafer temperature is held close to the ambient, using electrostatic wafer clamping. The capability of this process on the STS-ICP system is best illustrated by considering a number of demanding MEMS applications, however the typical performance of this process is summarised in the table below and the micrographs in Figures 6 and 8.

上一篇: 多晶硅表面改性技术以减少微观结构的粘附