Fiber to chip coupling is a critical aspect of any integrated photonic circuit. In terms of ease of fabrication as well as wafer-scale testability, surface grating couplers are by far the most preferred scheme of the coupling to integrated circuits. In the past decade, considerable effort has been made for designing effificient grating couplers on Silicon-on-Insulator (SOI) and other allied photonic platforms. Highly effificient grating couplers with sub-dB coupling performance have now been demonstrated. In this article, we review the recent advances made to develop grating coupler designs for a variety of applications on SOI platform. We begin with a basic overview of design methodology involving both shallow etched gratings and the emerging fifield of subwavelength gratings. The feasibility of reducing footprint by way of incorporating compact tapers is also explored. We also discuss novel grating designs like polarization diversity as well as dual band couplers. Lastly, a brief description of various packaging and wafer-scale testing schemes available for fifiber-chip couplers is elaborated.

Silicon photonics platform has emerged as a key driver for building the next generation of low cost on chip optical interconnects. This has been necessitated by an ever increasing need for multichannel high performance computing as well as large capacity data storage servers along with the requirement of low energy per unit bit power consumption. Several groups have now reported signifificant breakthroughs in demonstrating passive and active silicon (Si) based on chip photonic components. Primarily, three reasons are attributed to the preference of Si in integrated optics over other material platforms. The fifirst being SOI architecture, characterized by the high index contrast of silicon compared to its oxide that allows for sub-micron scale single mode wire waveguides. The second being a bandgap that enables wideband transparency window over the communication channel (1.3–1.6 µm). Finally, the availability of a mature silicon complementary metal oxide semiconductor (CMOS) microfabrication infrastructure which not only allows for implementing structures of nanoscale dimensions with high accuracy and repeatability, but also integrates them at a low cost, thereby allowing for large scale commercialization of photonic integrated circuits (PICs).

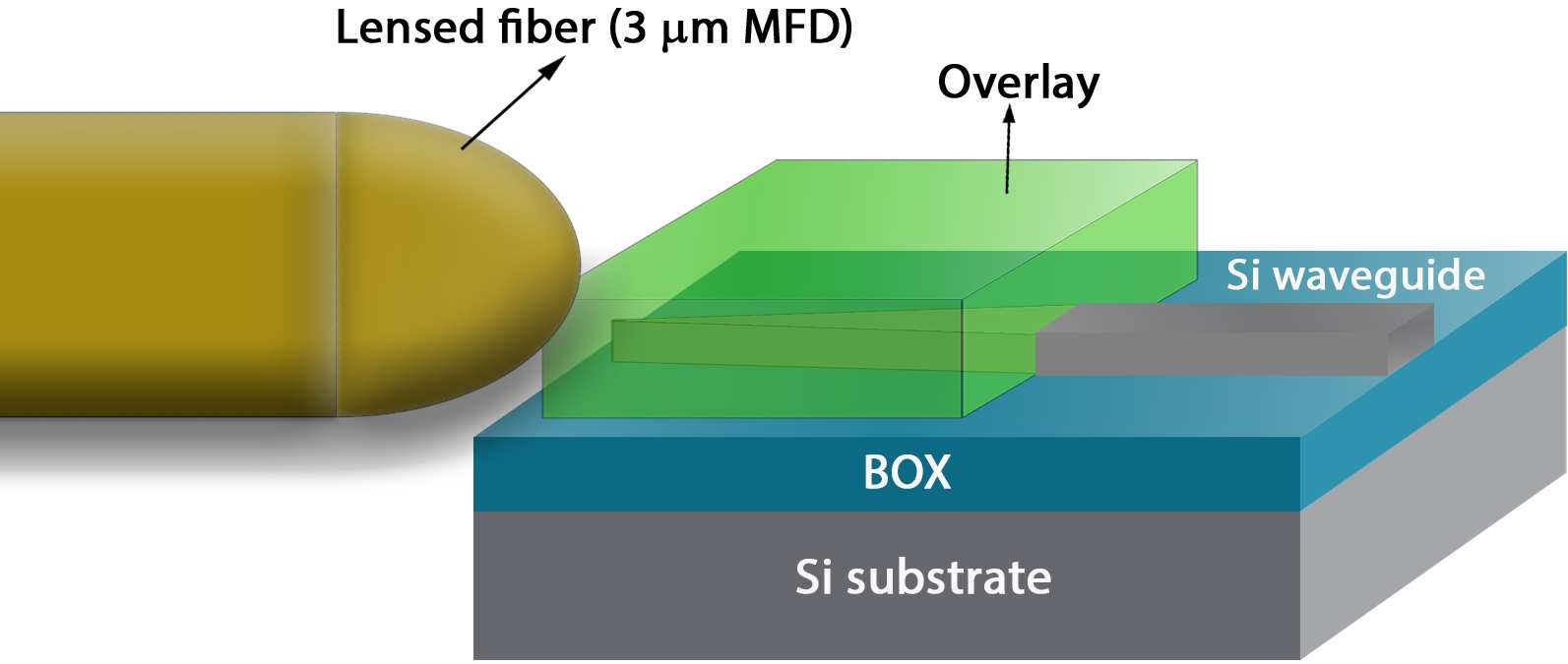

Photonic single mode waveguides are usually high index regions structured to support orthogonally polarized guided fundamental modes. There is consequently a considerable mismatch between the propagating vectors of light arriving from a low index cladding and that of a guided mode in a planar waveguide. This mismatch can be compensated by wave of a grating.

Fig1

The term Pclad also symbolises the device directionality. On a commercial SOI, the buried oxide (BOX) thickness is optimized to reflflect part of power from substrate back to waveguiding layer. However, even then, a substantial portion of power amounting to 25–30% is leaked to the substrate in a generic uniform grating coupler. We discuss the two principal ways that have been proposed to address this leakage.

There is a significant lateral mismatch between a surface grating coupler patch which is a multimode waveguide about 10–11 µm wide and that of a single mode Si waveguide (about 500 nm wide). The simplest way of addressing this mismatch is by way of incorporating an adiabatic linear taper between the grating patch and the wire waveguide. However, near perfect mode conversion would entail a taper of 700 µm length that would significantly increase device footprint. In the following section we shall discuss two ways of addressing the footprint problem i.e., by using either focusing gratings or compact tapers.

下一篇: 单晶硅纳米结构的金属辅助化学蚀刻技术