The heterogeneous integration of III–V devices with Si-CMOS on a common Si platform has shown great promise in the new generations of electrical and optical systems for novel applications, such as HEMT or LED with integrated control circuitry. For heterogeneous integration, direct wafer bonding (DWB) techniques can overcome the materials and thermal mismatch issues by directly bonding dissimilar materials systems and device structures together. In addition, DWB can perform at wafer-level, which eases the requirements for integration alignment and increases the scalability for volume production. In this paper, a brief review of the different bonding technologies is discussed. After that, three main DWB techniques of single-, double- and multi-bonding are presented with the demonstrations of various heterogeneous integration applications. Meanwhile, the integration challenges, such as micro-defects, surface roughness and bonding yield are discussed in detail.

The silicon (Si) complementary metal–oxide–semiconductor (CMOS) is the most dominant component in the semiconductor industry and the miniaturization of Si-CMOS is the main trend to further improve its speed, power consumption and production cost. However, as the Si-CMOS is scaled to smaller devices, the issues of device reliability, such as short channel effects and random fluctuations, become more severe, and the lithography and etching processes are more complex and costly . As the benefits of scaling subside, the device's performance will be more and more materials-driven. Thus, the development of new materials systems, which are compatible with the Si-CMOS platform, can be the next generation of semiconductor technologies to break the bottleneck of Si-CMOS scaling.

The performance improvement of a transistor is driven by the carrier mobility enhancement in the channel. The Group IV materials, such as SiGe and Ge, and the Group III–V compound materials, such as GaAs and InP, are well-known for their unique electrical properties and superior high mobility transistors. In addition, most of the III–V materials have direct bandgaps and are commonly used as lighting materials for LEDs and lasers. Compared to III–V materials, Si is an indirect bandgap material and it is difficult to fabricate an efficient lighting device using Si. Therefore, III–V materials-based light sources are used as a hybrid solution in a silicon photonics platform for data transmission. Meanwhile, this hybrid technology opens up numerous possibilities to develop new integrated circuit designs and applications in the fields of high-speed computation and sensing.

Epitaxial integration of growing III–V materials directly on Si substrates is the most desirable approach to integrate the III–V transistor with the Si platform. However, this method experiences many issues due to the large lattice mismatch and the difference in coefficient of thermal expansion (CTE) between the III–V compound semiconductor and Si. Thus, it remains a challenge to form thin III–V layers on Si while retaining excellent crystal quality. In addition, the growth of III–V materials requires a high temperature condition (650–1350 °C, depending on the materials systems).

In this section, various mainstream approaches in waferscale bonding will be reviewed, including DWB, surface-activated bonding, thermocompression bonding, eutectic bonding, glass frit bonding, adhesive bonding and anodic bonding. Among these bonding techniques, the DWB is the most promising approach for wafer-scale III–V on Si integration and Si-CMOS integrated devices due to its strong bonding strength, reliable bonding interface and low temperature processing conditions. This section will present these bonding techniques in more details.

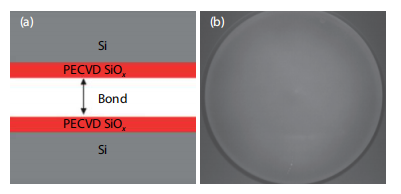

Fig1

Our group has successfully demonstrated the monolithic integration of Si-CMOS on SOI and III–V device layers on Si using wafer bonding and layer transfer techniques. In this section, we will discuss various DWB techniques, such as single-, double- and multiple-bonding techniques, and their possible applications. Since the high temperature growth of III–V wafers can be completed without the presence of Si-CMOS layers, DWB provides more temperature tolerance to pre-bonding processes. In addition, a plasma activation step is used to increase the surface hydrophilicity of bonding dielectric layers, and it can be performed at room temperature and atmosphere pressure. Therefore, DWB also avoids the thermal damage to Si-CMOS devices during the bonding processes.

The film stress can be determined by using a stress measurement system, it shows that the compressive stress in SixNy layers becomes tensile stress, and the tensile stress is very stable after 10 days of storage, as shown in Fig. 6. This also indicates that the SixNy layers block the moisture absorption after annealing. This can be explained by the higher density and mechanical strength, compared to SiO2 .