Copper direct bonding technology is considered to be one of the most promising approach for matching the miniaturization needs of future 3D integrated high performance circuits (3D-IC). In this study, we discuss the recent achievements in copper direct bonding technology with oxide/copper mixed surface and present the latest electrical and physical characterizations of chip to wafer bonding structures after annealing at 400°C and thermal cycling tests. In addition, electrical performance of chip to wafer bonding on 300mm wafers is also presented. Finally, thermo-mechanical finite element simulations showing the impact of the annealing conditions on the closure of the interface are shown.

Three-dimensional integration is considered as one of the most promising way to dramatically improve both the performance and the heterogeneity of electronic devices. This technology consists in stacking several wafers or chips together to achieve high interconnection density while reducing their length. To obtain functional bonded devices, main key steps like surface preparation, alignment, bonding, thinning and Through Silicon Via (TSV) connections must be mastered. The two main bonding techniques allowing simultaneous mechanical and electrical connection are thermo-compression bonding and metallic direct bonding. While both techniques have their advantages, copper direct bonding appears to be the most encouraging way to achieve very high interconnection density. Previous studies have demonstrated the relevance of the Wafer to Wafer (WtW) copper direct bonding technology with robust electrical performance on 200mm wafers. Nevertheless, a WtW strategy entails significant drawbacks, such as a constant die footprint between tiers and the impossibility to ensure high production yields without prior Known Good Dies (KGD) selection. For these reasons, a Chip to Wafer (CtW) strategy has been carried out and assessed on 200mm and 300mm wafers environments, high density interconnects being generally required for advanced CMOS node. In this paper we present the latest electrical characterizations of 200mm CtW bonding after annealing at 400°C and Thermal Cycling (TC) tests, and we compare them to 200mm WtW bonding technology. In addition, electrical performances of 300mm CtW bonding were also investigated. Finally, thermo-mechanical finite element simulations were done to investigate different annealing conditions and their impact on the closure mechanism of the bonding interface.

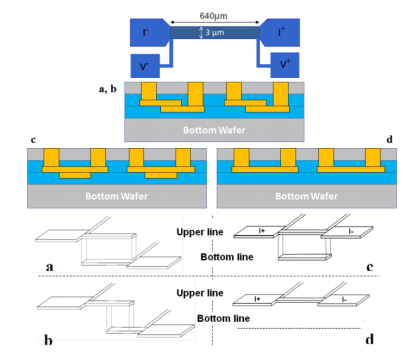

The two main structures used to characterize the electrical resistance of the Cu-Cu bonding interface were bonded and stand-alone NIST (National Institute of Standard Technology) and daisy chains structures. A schematic description of the bonded and stand-alone NIST structures can be found in the Fig. 1. The stand-alone NIST (d) were used to first extract the copper resistivity and then to calculate the theoretical resistance for the bonded structures. The contact area of these structures is 640 x 3µm² for the NIST (a) and (c), and 340 x 3µm² for the NIST (b). The probe pads of the NIST (a) and (b) are situated on two different layers, which forces the current to pass through the bonding interface during the electrical characterization. On the contrary, the contact pads of the bonded structure NIST (c) are on the same metal layer. Therefore, if the contact resistance is too high, in the case of a poor bonding quality for instance, the current would flow only in the upper line without crossing the bonding interface.

Fig1

The fabrication was performed at CEA Leti on 200mm silicon wafers, based on a classical damascene process. After 500nm thick opening into an 800nm thick deposited SiO2 layer, TiN diffusion barrier and Cu seed layers were deposited. Cu filling was carried out by electroplating and then annealed at 400°C. After an optimized CMP surface preparation, wafers were bonded at room temperature, atmospheric pressure and ambient air. In order to strengthen the bonding interface, the stacked wafers were annealed at 400°C during 2 hours. To allow the direct probing at a wafer level, several technological steps are performed on the bounded wafers: top wafer thinning down to 50μm, via etching and realization of a redistribution layer (RDL). Finally, a BCB passivation and a UBM layers were processed (Fig. 3).

Chip to wafer bonding offers a lot of advantages from design and integration points of view, but various questions about the mechanical strength or the reliability of the stacks must be investigated. This is why we conducted for the first time thermal cycling tests on non-thinned CtW bonding structures, based on a classical JEDEC standard with 1000 cycles at ambient pressure and a temperature cycling between -40°C and +125°C. In order to verify the structural integrity of the interface, electrical characterizations and SEM images were realized after the TC tests. As shown on the Fig. 8, no increase of the resistance or dramatic failure caused by major structural deformations, like voids or delamination, was observed on the NIST and daisy chain structures. This encouraging result indicates the high mechanical strength of non-thinned bonded chips, but in order to fully address the mechanical reliability question of CtW stacks, additional investigations must be conducted in the future, including TC tests on thinned-down chips with a complete BEOL and thermo-mechanical simulations.

The difference between experimental and theoretical resistance for the DC5 node is 4.7mΩ this time, which proves a robust bonding quality, the bonding interface having little impact on the global resistance. This result is all the more interesting as the bonded samples come from two different technologies, demonstrating the feasibility of heterogeneous integration with the direct bonding technology. Moreover, by comparing the resistances of all the NIST present on the 19 bonded chips, we did not notice any significant variations (Fig. 10). Indeed, the standard deviation for the NIST (a) and (b) is 3.39% and 1.47% respectively, which is in accordance with industry standards regarding interconnections. This result implies high fabrication homogeneity and confirms that the CtW bonding process gives good electrical performances whether the chip is bonded on the edge or at the center of the 300mm wafer.

The simulation scenario was divided into 3 main steps. The first one consisted in the approach of the top part toward the bottom one, initially separated from 1µm, in order to initiate the bonding at ambient temperature. During the second step the annealing at 400°C occurred, which led to the copper dilatation and thus the complete or partial closure of the copper interface. Finally during the last step the parts assembly cooled down, going from 400°C to 20°C.

上一篇: 硅太阳能电池的介电表面钝化

下一篇: 晶圆级的金刚石纳米和量子技术