我们通过键合薄的绝缘体上硅晶片来制造具有25纳米二氧化硅槽层的水平硅槽波导。在从键合结构的一侧去除硅衬底和掩埋氧化物之后,光栅耦合波导和环形谐振器被部分蚀刻到硅/二氧化硅/硅器件层中。光栅在1550纳米处显示出高达23%的效率,并且环形谐振器被测量为对于最低阶横向电模式具有接近42 000的负载质量因子,对应于15 dB/cm的传播损耗。还观察到泄漏的最低阶横向磁模式,传播损耗为44分贝/厘米。2009年美国物理研究所。

介绍

在过去的几年里,硅光子技术使得无源波导和谐振器的密集集成成为可能。硅光子学的研究正在解决实现芯片级硅基有源器件的挑战。特别是,在硅芯片上产生和放大电信频率的光的概念引起了极大的兴趣。一种有希望的方法是将有源增益材料直接集成到硅波导层中。使用具有硅/槽/硅结构的槽波导,可以利用对称性来最大化导模与有源槽材料的重叠,并潜在地利用硅层进行电注入。

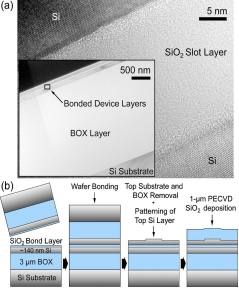

虽然绝缘体上硅SOI中的垂直槽波导已经被证明,4,5使用传统的薄膜沉积工艺很难填充高纵横比的槽。因此,我们相信以水平配置制造结构更适合于使用沉积的活性槽材料的应用。在本文中,我们提出了一种制造硅基水平缝隙波导的技术,该技术与沉积的活性材料兼容,但不需要随后沉积有损耗的非晶或多晶硅层。我们的工艺使用室温共价晶片键合将SOI晶片的硅器件层转移到第二个SOI晶片上,其间有薄的二氧化硅槽层,如图1所示。1.所得的层状结构在槽的上方和下方都具有单晶硅层。

实验

为了制造我们的晶片键合缝隙波导,我们从市场上可买到的SOI晶片开始,该晶片由SOITEC制成,具有3 m掩埋氧化物层和250 nm厚的轻掺杂1015 cm3 p型硅器件层,该硅器件层被减薄然而,我们测量了相关器件区域小于5 nm的变化。使用干氧化法生长薄的热氧化结合层。然后使用Tong等人的方法制备晶片的裂开片并结合.具体地说,在1∶0.2∶5的改良RCA溶液中清洗这些片

H2O2:NH4OH:H2O,在去离子水中漂洗,并在1:200 HF:H2O中浸泡10 s。然后将样品在250℃下烘烤,在RCA溶液中再次清洗,并在O2压力为115毫托的400瓦O2等离子体中处理。在接触并在室温下放置至少24小时后,样品在N2 1100℃下退火。

图。1.在线着色制造结构的横截面透射电镜显微照片,显示所有嵌入层和粘合槽区域的放大图像。制造工艺流程示意图。

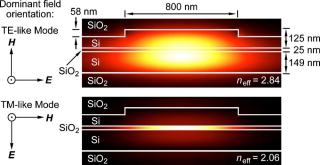

图。2.彩色在线图所示为在1550纳米处,在类热电和类热电模式下计算出的功率分布。

在20%氢氧化钾溶液中蚀刻。通过聚焦离子束研磨从样品中提取薄层,并用高分辨率透射电子显微镜TEM进行表征,如图1所示。1a . 观察到的层尺寸与图2中给出的椭偏光谱测定法测定的一致。透射电镜中晶格条纹的出现表明,硅层明显是单晶的。

使用电子束光刻和SF6/C4F8反应离子蚀刻工艺制造了具有光栅耦合通孔和分支端口的环形谐振器。光栅被设计为50纳米的深度,以便将它们的特征耦合长度与用于器件测试的激光束的聚焦光斑尺寸相匹配,7并且使用椭偏法确定实际蚀刻深度为58纳米。选择800纳米的波导宽度,以确保仅支持最低阶横向电热电模式和热电模式。最终的波导横截面几何形状如图2所示。2.谐振器器件布局如图2所示。3连同蚀刻结构的扫描电子显微镜扫描电镜图像。光栅宽30米,长50米,间距660纳米。光栅和较窄的波导之间形成500米长的线性过渡。环被图案化为具有400 m的大内径,以避免弯曲损失,在端口和环之间限定了8和1 m的耦合间隙。最后,使用等离子体增强化学气相沉积,用1 m二氧化硅涂覆整个结构。

结论

总之,我们展示了具有单晶硅波导层的晶片键合水平缝隙波导。通过使用表面浮雕光栅将1550纳米的光耦合到部分蚀刻的波导环形谐振器中,我们能够获得槽结构的最低阶TE和TM模式,并确定波导传播损耗。当与通过类似工艺制造的窄单层SOI波导相比时,测量到的15 dB/cm的TE模式损耗表明槽中的键合界面在1550 nm附近没有导致压倒性的衰减。TM模式的44分贝/厘米的较高损耗是由于泄漏到波导周围的平板中,应该在未来的器件中通过修改器件几何形状来解决。总的来说,我们相信这些结果表明,晶片键合是将各种硅基缝隙材料直接集成到SOI波导中的可行方法。

下一篇: 醇类添加剂对 KOH溶液蚀刻特性的影响