The reach and impact of the Internet of Things will depend on the availability of low-cost, smart sensors—“low cost” for ubiquitous presence, and “smart” for connectivity and autonomy. By using wafer-level processes not only for the smart sensor fabrication and integration, but also for packaging, we can further greatly reduce the cost of sensor components and systems as well as further decrease their size and weight. This paper reviews the state-of-the-art in the wafer-level vacuum packaging technology of smart sensors. We describe the processes needed to create the wafer-scale vacuum microchambers, focusing on approaches that involve metal seals and that are compatible with the thermal budget of complementary metal-oxide semiconductor (CMOS) integrated circuits. We review choices of seal materials and structures that are available to a device designer, and present techniques used for the fabrication of metal seals on device and window wafers. We also analyze the deposition and activation of thin fifilm getters needed to maintain vacuum in the ultra-small chambers, and the wafer-to-wafer bonding processes that form the hermetic seal. We discuss inherent trade-offs and challenges of each seal material set and the corresponding bonding processes. Finally, we identify areas for further research that could help broaden implementations of the wafer-level vacuum packaging technology.

Miniaturized semiconductor sensors are at the heart of the next wave of interconnectivity—the transition from the “Internet of People” to the Internet of Things (IoT). To realize the full potential of IoT, sensor fabrication methods must continue to reduce the size, weight, power, and cost (SWaP-C) of the sensor component and system. The same trend needs to apply to sensor packaging, which currently accounts for as much as 80% of the overall cost and form factor. To make IoT a reality, the industry needs to adopt packaging methods that reduce SWaP-C.

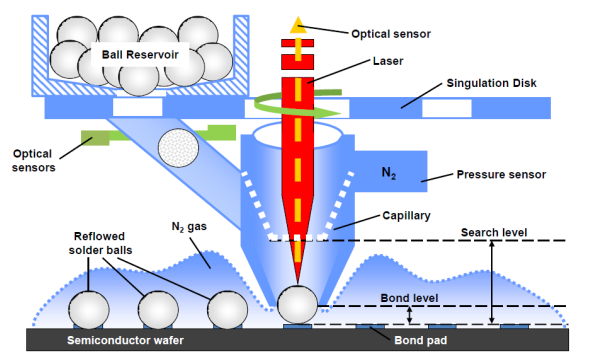

Many of semiconductor sensors, especially those in the category of microelectromechanical systems (MEMS), require a vacuum environment to achieve the desired sensitivity. In this group are inertial sensors, thermal imagers, pressure sensors, and resonance devices. The vacuum environment is typically established soon after the sensor fabrication to protect the sensor during downstream assembly. To reduce SWaP-C, vacuum packaging has shifted from serial, die-level approaches to massively parallel, wafer-level vacuum packaging (WLVP). In a WLVP process, a wafer containing a semiconductor sensor die (i.e., device wafer) is bonded under vacuum to a passive lid wafer or to another device wafer containing part of the sensor architecture.

Fig1

Electroplating of the Au0.8Sn0.2 eutectic alloy through a resist pattern is an attractive deposition method due to the composition and geometric control that it affords. However, the approach has significant challenges. Due to inherent non-uniformities of the electric fifield in any plating cell, electroplating deposition rates vary across the wafer. These fifield variations, in combination with relatively large differences in electrode potentials between Au and Sn, make it difficult to control the relative amounts of the metals in the deposit. Although a number of groups have worked on developing electroplating solutions, information on compositional uniformity is very limited. The limited data suggest that the composition uniformity range is as much as 6.6% from wafer to wafer. This range results in melting temperature differences as high as 50 ◦C, making it difficult to create a reproducible bonding process.

Au0.82Si0.18 eutectic bonding, originally developed and adopted as a die attach process, has more recently been demonstrated for transfer printing of light emitting diodes (LEDs) and as a wafer bonding method for absolute pressure sensors, a MEMS Pirani vacuum gauge with CMOS elements , and other MEMS and smart sensors using surrogate wafers . In this approach, Au is deposited by evaporation, sputtering, or electroplating. The source of Si is a deposited Si layer or the Si substrate itself. For smart sensor applications, diffusion barriers are included to prevent Au diffusion into the CMOS device layers. During bonding, the wafers are heated to around 400 ℃, and the Au and Si undergo solid-state diffusion until the eutectic composition is reached. Since solid-state diffusion is required, the Au and Si layers are typically formed on the same wafer, ensuring intimate contact between the layers. As shown in Figure 5, once the Au0.82Si0.18 liquid forms, in this case, on the cap wafer, bonding occurs between the liquid on the cap wafer and the mating Si or Au surfaces on the device wafer. Advantages of this approach include a readily available materials set, ease of deposition, compatibility with MEMS release and cavity etch processes, and the lack of a native oxide on the Au surface.

上一篇: 金属沉积过程中晶圆制造的颗粒减少

下一篇: 界面电荷对硅基碳化硅功率器件开发的影响