Si is the material from which nearly all classical electronic integrated circuits are fabricated. While SOI is nowadays used for the fabrication of high-end electronic integrated circuits, the use of the material for photonic applications is being intensively studied1-5. An SOI wafer (commercially available up to 300 mm in diameter) consists of a Si layer on top of a buried SiO2 layer, fabricated on a Si substrate. While in electronic integrated circuits the presence of the buried SiO2 layer improves transistor performance, in photonic applications it is used to create a high vertical refractive index contrast between the Si top layer (nSi = 3.45) and the SiO2 (nSiO2 = 1.45), that is able to guide near-infrared light (λ >1.1 µm) in the Si top layer by total internal reflection. A large omnidirectional index contrast can be obtained by laterally etching the Si top layer to obtain a Si photonic wire surrounded by low refractive index air and SiO2 cladding material. In order to restrain the propagation of light in the optical waveguide to a single optical mode at the telecommunication wavelengths of 1.3 µm and 1.55 µm, a typical maximum waveguide cross-section of 0.1 µm2 is required.

Two techniques for semiconductor wafer bonding have been investigated. In the first approach, adhesive semiconductor wafer bonding18 using the thermosetting polymer divinylsiloxanebenzocyclobutene (DVS-BCB) as a bonding agent has been developed19, while in the second approach, molecular wafer bonding has been investigated20. Both approaches are schematically outlined in Fig. 3.

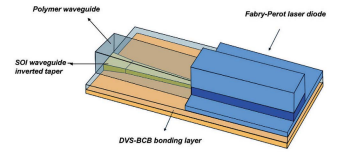

In adhesive wafer bonding, an oligomer solution of DVS-BCB is spin coated onto the processed SOI waveguide circuit. This process planarizes the waveguide topography. After spin coating, a baking step at 150°C removes residual solvent in the spin-coated film, while a short baking step at 250°C transforms the liquid DVS-BCB into a sol/gel rubber by partial polymerization. The preparation of the InP/InGaAsP epitaxial layer surface is optimized to achieve a high bonding strength. A HF surface treatment improves the bonding strength by chemical modification of the III-V surface. After attachment of the III-V dies, the wafer stack is cured at 250°C for 1 hour to polymerize the DVS-BCB completely. A uniform pressure is applied to the wafer stack during curing to achieve a close contact between both surfaces. DVS-BCB was chosen as the bonding agent because of its optical transparency, excellent planarization properties, low curing temperature, the fact that no outgassing occurs during cure, and its high glass transition temperature (>350°C), which determines the available post-bonding thermal budget for the fabrication of the laser diodes.

In the molecular wafer bonding approach, the processed SOI wafer surface is coated with an SiO2 cladding layer and planarization is achieved by chemical mechanical polishing (CMP). Subsequently, the III-V epitaxial layer structure is coated with SiO2 and, if needed, a touch-polish CMP step can be used to reduce the surface microroughness, necessary to achieve molecular bonding. This is because of the short range of the van der Waals attraction forces on which the molecular bonding relies. For the approach to be successful, the surfaces of both wafers must be in contact on the atomic scale. Typically, a root mean squared (RMS) microroughness of 0.5 nm is required to achieve molecular adhesion. After surface planarization and reduction of the microroughness by CMP, both wafer surfaces are chemically activated. Hydrophilic SiO2 surfaces can be achieved by both wet chemical treatment and plasma activation. Van der Waals interactions between both surfaces is achieved when the two activated wafer surfaces are attached to each other because of the presence of a H2O interface layer, which is readily adsorbed at the wafer surface. During annealing of the bonded stack, H2O molecules are removed from the bonding interface, leaving a covalent bond between the SiO2 surfaces. In other work, the processed SOI waveguide is not planarized and the III-V die is directly bonded onto the SOI waveguide topography, leading to air gaps in the bonded stack.

Although semiconductor wafer bonding is performed in a cleanroom environment, special care has to be taken to avoid the inclusion of particles at the bonding interface as they can create large unbonded areas. Typically, a particle with a height h trapped at the bonding interface results in a circular unbonded area with a radius of about 5000h20.

Fig1

While this approach requires a dedicated structure to couple light from the III-V layer to the SOI waveguide circuit, because of the presence of the DVS-BCB bonding layer, the use of hybrid waveguide structures, in which the laser waveguide mode is partially located in the Si waveguide core while it experiences gain from the III-V layer, has been demonstrated as well in other work21. This approach, however, relies on a relatively thick Si waveguide core layer (690 nm). Scaling this approach to Si waveguide core layers λ/2n thick as used in this work, which are required for high density integration, is not straightforward.