摘要

本文报道了有关对碳化硅(SiC)进行深度刻蚀的研究,以实现在相同厚度的碳化硅基片上形成隔离的深凹槽。本文将等离子体刻蚀和电化学刻蚀结合应用于n型SiC层上方的p型SiC。使用电镀沉积的镍掩模获得均匀且光滑的SiC等离子体刻蚀表面。这一步骤允许将未受保护的SiC刻蚀至30微米。选择性的导电电化学刻蚀可获得更高的刻蚀深度。p型层将保持惰性并作为终止层,而n型层将被腐蚀。最后,本文获得了深度约为80微米的刻蚀,为开始制造垂直功率集成SiC器件开辟了前景。

一、介绍

碳化硅被归类为世界上最坚硬的材料之一。碳化硅(SiC)的硬度很强,在制造半导体器件时需要采用困难的技术,但如今在电力电子领域已经达到了一定的成熟水平。与更经典的硅相比,由于其具有较大的带隙和能够支持高电场的能力,SiC功率器件在高温操作、快速和高电压性能方面优于硅。

碳化硅的使用提高了电力电子产品的可靠性,同时将多个功率器件集成在相同的碳化硅芯片中有望提高开关操作速度并降低功率损失。为了制造集成功率电路,需要在碳化硅微电子系统制造方面开发新技术。在将多个功率器件集成在相同的碳化硅芯片中的过程中,实现深度刻蚀厚度是技术关键之一,以便实现绝缘。在垂直设备集成的案例中,需要刻蚀整个碳化硅基板(数百微米)。

先前的研究已经解决并报道了仅几微米的碳化硅的经典等离子体刻蚀。在这种情况下,已经发现在碳化硅等离子体刻蚀期间使用Ni作为掩模可以减少微掩蔽效应,此外,与其他硬掩模(如金属铝)相比,在SF6/O2反应离子刻蚀(RIE)等离子体中,它对碳化硅具有良好的选择性,高达约50:1。在RIE和/或感应耦合等离子体(ICP)刻蚀过程中消耗Ni掩模可能是碳化硅刻蚀的速率限制步骤。为了增加刻蚀深度,需要高厚度的Ni层,而经典的物理气相沉积(PVD)方法(如蒸发或溅射)难以制备。我们之前工作的创新性在于在碳化硅基片上显示了高粘附性的电镀Ni金属层,允许复制等离子体刻蚀而不消耗Ni金属掩模。这种粘附性金属层是通过在碳化硅基片上自然呈现的薄硅氧化物层上生长钯纳米颗粒而稳定的。

我们使用优化后的感应耦合等离子体/反应离子刻蚀工艺,获得了相当大的碳化硅刻蚀厚度,高达30微米。然后,为了增加碳化硅的刻蚀深度,使其超过等离子体刻蚀的极限,我们将所进行的等离子体刻蚀与电化学刻蚀进行了比较。根据Shor等人报告的研究[6],本文进行了电化学刻蚀并获得了超过80微米的刻蚀厚度。

二、实验

1、3-氨基丙基三乙氧基硅烷(APTES)、功能化步骤、Pd纳米颗粒的生长和镍电镀

3-氨丙基三乙氧基硅烷(APTES)通过与经O2等离子体处理形成的羟基官能团相连,附着在碳化硅(SiC)表面天然存在的SiO2薄层上。以前为了将APTES吸附到氧化铝上,对该方法进行了研究[7]。将1毫升APTES分散在20毫升甲苯溶液中。将SiC基片浸泡在含有硅烷前驱体的甲苯溶液中24小时。氨基硅烷功能化的SiC表面最后用甲苯清洗,在空气中干燥,并保存在手套箱中以进行下一步。

另一边缘的胺官能团现在可以自由地参与进一步的表面改性反应(图1 A)。

将底物浸泡在含有0.5 g/L PdCl2和20 mL 37%盐酸的水溶液中,在室温(RT)下,活化APTES覆盖的底物10 min。

图1 (A) APTES功能化的碳化硅基片 (B)电镀在功能化碳化硅基片上的镍层 (C)在镍层上沉积光刻胶,进行光刻和湿法刻蚀以获得目标图案

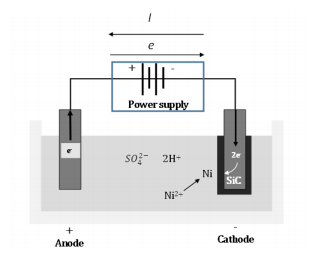

电镀液由1750毫克(Ni(NO3)26H2O),1500毫克(NiSO4.6H2O)和2600毫克硼酸组成,溶于500毫升水中。活化样品通过自催化反应形成金属层,该金属层从溶解在溶液中的镍离子沉积而来,在RT下进行2分钟的施加电流为0.05安(图2)。

图2 在碳化硅衬底上电镀镍的示意图图像

2、镍掩模图案化和碳化硅蚀刻

为了对Ni层掩模进行图形化处理,旋转涂布看似简单的过程却实现了AZ9260正性光刻胶的厚而均匀涂覆(图1C)。

涂覆后,光刻胶薄膜在115℃下退火15分钟。使用光学光刻掩模对准机(SUSS MicroTec MJB4)进行UV光曝光75秒,与玻璃铬掩模紧密接触。曝光后:将基片浸入AZ 726MIF显影液中。使用磷酸、硝酸和乙酸混合溶液蚀刻未覆盖金属区域,将基片在60℃下浸泡2小时,然后用丙酮去除光刻胶。

在Ni层上也沉积了硅薄层,以增加Ni副产物的挥发性,避免了在碳化硅等离子体刻蚀过程[4]中的微掩蔽。采用Plassys MEB400机,低压1.6×10−6mbar。

使用ICP/RIE Plassys MU400反应器对图案化碳化硅基片进行蚀刻。所用反应器由两个电源组成:等离子体增强反应离子刻蚀(RIE)以在基片表面形成电离的等离子体,感应耦合等离子体(ICP)以增强活性物种的密度。蚀刻气体为SF6和O2。氟化物离子冲击碳化硅表面并断裂硅碳键,生成氟化硅(SiFx)和氟化碳(CFx)挥发性物质。氧原子增强氟原子的生成并与碳层相互作用,生成挥发性一氧化碳(COx)物质。

3、扫描电镜表征

利用光学显微镜(尼康日蚀)和日立SU8030设备的场发射扫描电镜(SEMFEG)对其形态、图案掩模和蚀刻沟槽进行了研究。

三、结果与讨论

1、表面活化

在SiC基片上应用APTES处理,通过O2等离子体处理在表面上的天然硅氧化物层上形成羟基,以接枝硅烷。APTES容易与羟基反应,形成自组装单层(SAM)的有机分子。

我们遵循相同的步骤在SiC表面创建Pd胶体,作为Ni电镀的活性催化剂。Ni涂层是由溶液中溶解的Ni离子形成的(图3)。

图3 在Pd活化的碳化硅基底上电镀镍的光学图像

2、动力学蚀刻和表面形态

在碳化硅基底表面沉积Ni后,使用∼12µm AZ9260光刻胶,通过确定刻蚀碳化硅所需的裸露金属面积,得到了所需的Ni图案,如图1c所示。

我们使用的ICP/RIE等离子体反应器蚀刻参数包括:8 mTorr的工作压力、25 sccm的SF6气体流量和7 sccm的O2气体流量、1000W的ICP功率和180W的RIE功率(430V偏压)。这些参数是从我们以前对RIE反应器所做的研究,经过调整后适用于我们的ICP/RIE反应器。

四、结论

在活化的SiC基片上进行了Ni电镀处理。使用APTES对SiC进行活化处理,随后进行Pd处理,可以获得更致密且坚固的Ni金属表面,SiC基片上的Ni层即使在等离子蚀刻工艺之后仍然保持刚性和稳定性,除了几百纳米的厚度之外,不会对其产生影响。通过应用两次30分钟的等离子蚀刻工艺(使用SF6/O2),获得了可观的SiC蚀刻厚度,约为30微米。然而,通过使用电化学蚀刻,可以达到高达80微米的蚀刻厚度。此外,我们观察到在电化学蚀刻中增加施加电流会提高蚀刻表面的孔隙率。这项研究为通过进行深蚀刻来隔离器件从而获得集成的多终端芯片提供了可能性。