ABSTRACT:

Ultra-wide bandgap semiconductor devices based on β-phase gallium oxide (Ga2O3) offer the potential to achieve higher switching performance, efficiency, and lower manufacturing cost than today’s wide bandgap power electronics. However, the most critical challenge to the commercialization of Ga2O3 electronics is overheating, which impacts the device performance and reliability. We fabricated a Ga2O3/4H-SiC composite wafer using a fusion-bonding method. A low temperature (≤ 600°C) epitaxy and device processing scheme was developed to fabricate MOSFETs on the composite wafer. The low-temperature grown epitaxial Ga2O3 devices deliver high thermal performance (56% reduction in channel temperature) and a power figure of merit of (~300 MW/cm2 , which is highest among heterogeneously integrated Ga2O3 devices reported to date. Simulations calibrated based on thermal characterization results of the Ga2O3-on-SiC MOSFET reveal that a Ga2O3/diamond composite wafer with a reduced Ga2O3 thickness (~1 μm) and thinner bonding interlayer (<10 nm) can reduce the device thermal impedance to a level lower than today’s GaN-on-SiC power switches.

β-phase gallium oxide (Ga2O3) is an ultra-wide bandgap (UWBG) semiconductor (EG~4.8 eV), which promises significant improvements in the performance and manufacturing cost over today’s commercial wide bandgap (WBG) power electronic devices based on GaN and SiC.1 During the past half-decade, significant progress has been made in the Ga2O3 bulk material synthesis (i.e., only Ga2O3 offers melt-grown single crystal substrates like Si wafers, among today’s WBG and UWBG semiconductors), epitaxial growth, doping, and the development of homoepitaxial device architectures.UWBG Ga2O3 electronics give promise to allow designers to use fewer devices and smaller passive components in power electronics circuits. 4 Power conversion systems for electric vehicles and charging stations, renewable energy sources, and smart grids will benefit from the Ga2O3 device technologies.

RESULTS AND DISCUSSION

2.1. COMPOSITE WAFER FABRICATION

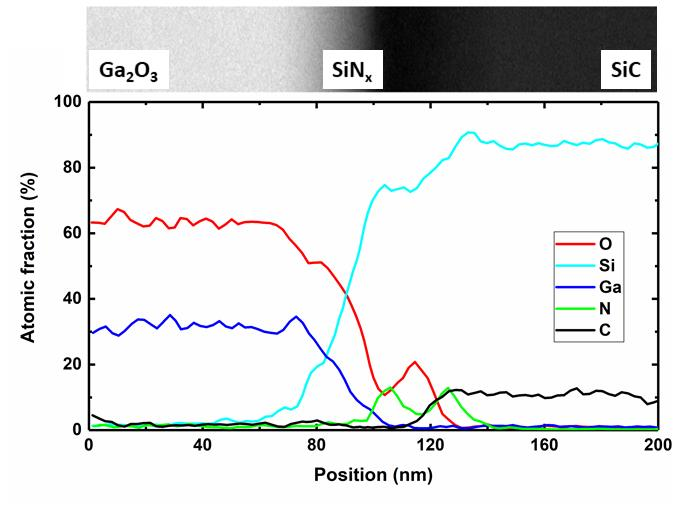

In our previous work, a Ga2O3/4H-SiC composite wafer was fabricated using a fusion bonding process. Here we provide a summary of the fabrication process and structure of the composite wafer. 15 nm of SiNx was coated on both a (010)- oriented Fe-doped 25 mm-diameter Ga2O3 wafer (which is the preferred orientation to achieve higher thermal performance) and a 50 mm-diameter 4H-SiC wafer. To initiate fusion bonding, the wafer surfaces were activated in oxygen plasma and joined at room temperature. After this, the integrated material stack was cured at 215°C in a N2 convection oven. The bonded Ga2O3 wafer was thinned down using a series of lapping plates and a diamond abrasive (9 µm, 3 µm, and 0.25 µm diamond grit size). A silica-based chemical-mechanical polishing (CMP) process was used to achieve an epitaxial-ready surface. A critical advantage of the wafer bonding approach over heteroepitaxy directly on SiC is that it allows subsequent homoepitaxial growth of highest quality crystalline films without threading dislocations, because the starting material is a highest quality melt-grown Ga2O3 substrate. The final thickness of the Ga2O3 was measured via cross-sectional scanning electron microscopy (SEM) of a specimen prepared by focused ion beam (FIB) milling. Scanning transmission electron microscopy (STEM) imaging and energy-dispersive X-ray spectroscopy (EDX) mapping were respectively used to evaluate the quality and chemistry of the Ga2O3/SiC interface. As shown in Figure 1, a 10 nm thick SiOx layer was unintentionally formed between the SiNx bonding layers, contributing to the effective thermal boundary resistance at this interface.

Figure 1: High angle annular dark field STEM image near the Ga2O3/4H-SiC interface and EDX line map across the Ga2O3/4HSiC interface.

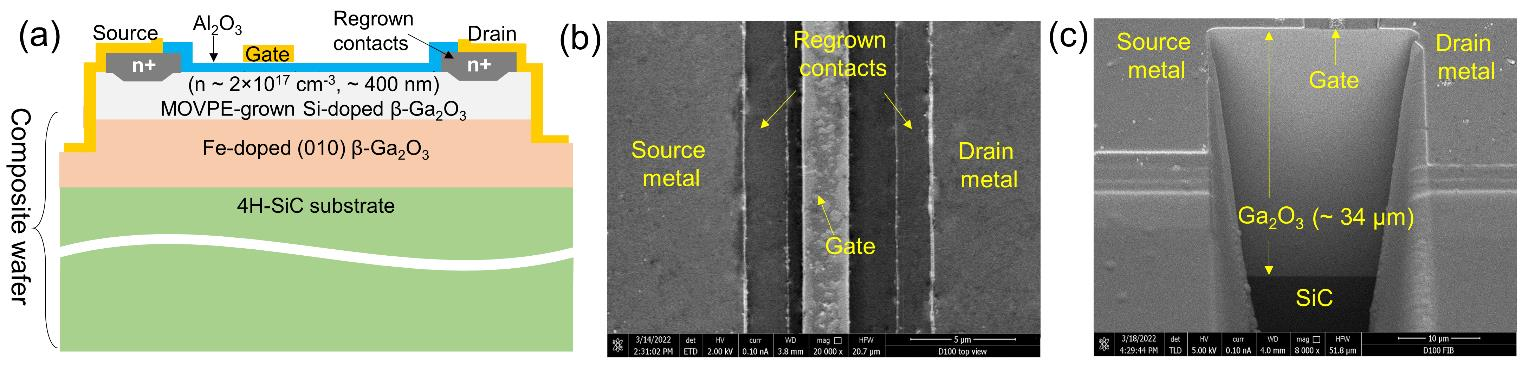

To maintain the structural integrity of a composite substrate, it is of critical importance to limit the maximum temperature that occurs during the multiple processing steps associated with device fabrication. For this reason, a low temperature device processing scheme was developed that keeps the maximum temperature of the entire process below 600°C. It should be noted that current growth techniques for other electronic grade WBG and UWBG materials systems such as GaN, SiC, and AlGaN do not allow this. Device fabrication began with the epitaxial growth of a Si-doped channel. The composite substrate was solvent cleaned in sonication baths of acetone, isopropyl alcohol and deionized (DI) water. Next, the substrate was dipped in a hydrofluoric acid solution for 15 minutes and then cleaned using DI water. After cleaning, the sample was loaded into a metalorganic vapor-phase epitaxy (MOVPE) reactor and a (010) oriented Si-doped Ga2O3 epilayer (~400 nm thick) was grown at 600°C. 35 An Agnitron Agilis vertical quartz tube MOVPE reactor was used with triethylgallium (TEGa) and O2 as the precursor gases, argon as the carrier gas, and diluted silane for doping. From Hall measurements, the room temperature channel sheet charge and mobility were found to be 1.3×1013 cm-2 and 94 cm2 /Vs, respectively. Due to the sufficient adatom diffusion lengths at this growth condition (i.e., temperature and molar gas flow fluxes), an atomically smooth surface morphology(RMS roughness of ~0.5 ± 0.1 nm) was maintained and single crystal films with high crystalline quality and transport properties were realized. The low temperature MOVPE growth process helps minimize the potential risk of debonding of the composite wafer due to the thermal expansion mismatch between the Ga2O3 and 4H-SiC materials. 15 A crosssectional schematic of a Ga2O3 metal-oxide-semiconductor field-effect transistor (MOSFET) fabricated on the composite wafer is shown in Figure 2 (a). Device processing started with mesa isolation using a patterned Ni/SiO2 hard mask and directional dry etching, i.e., inductively coupled plasma - reactive ion etching (ICP-RIE) SF6-Ar (600W ICP, 150 RF powers – 45 nm/min etch rate for Ga2O3).36,37 This was followed by source-drain region patterning using the same Ni/SiO2 patterning process and contact region recessing using a low power ICP-RIE SF6-Ar (150W ICP, 50 RF powers – 1.5 nm/min etch rate for Ga2O3).38 After selectively wet etching Ni, the sample with the patterned SiO2 mask was loaded into the MOVPE reactor for ohmic contact regrowth. A heavily Si-doped n+ (estimated 1.4×1020 cm-3 ) Ga2O3 layer was grown at 600°C with an approximate thickness of 100 nm. 37 The sample was then cleaned in an HF solution and the regrowth mask including regrown Ga2O3 was selectively removed from all regions except the source-drain regions. This was followed by ohmic metal evaporation of Ti/Au/Ni (20/100/50 nms) on the n+ regions by photolithography and lift-off. The contacts were then annealed in a rapid thermal processing (RTP) furnace at 450°C for 1.5 mins in a N2 ambient. A thermal atomic layer deposition (ALD) grown Al2O3 layer (at 250°C) with a target thickness of 25 nm was blanket deposited to form the gate insulator. Then, a Ni/Au/Ni (30/100/30 nm) metal stack was evaporated to form the gate electrode. Finally, the Al2O3 over the source-drain metal pad regions was removed using a photoresist mask and CF4-O2-N2 ICP-RIE dry etching. It is to be noted that (apart from benefitting from the low temperature processes), the composite substrate shows strong ruggedness against standard device processing steps (such as ultrasonication in solvents, acid cleaning, wet and dry etching, and dielectric/metal deposition), as well as patterning processes. This confirms its compatibility with standard device processing methods used to fabricate homoepitaxial devices on bulk Ga2O3 wafers.

Figure 2: (a) A cross-sectional schematic of a Ga2O3 MOSFET fabricated on the composite substrate. (b) Plan-view SEM image of a final device structure. (c) Cross-sectional SEM image of the same device showing the thickness of Ga2O3 layer.

DEVICE THERMAL CHARACTERIZATION

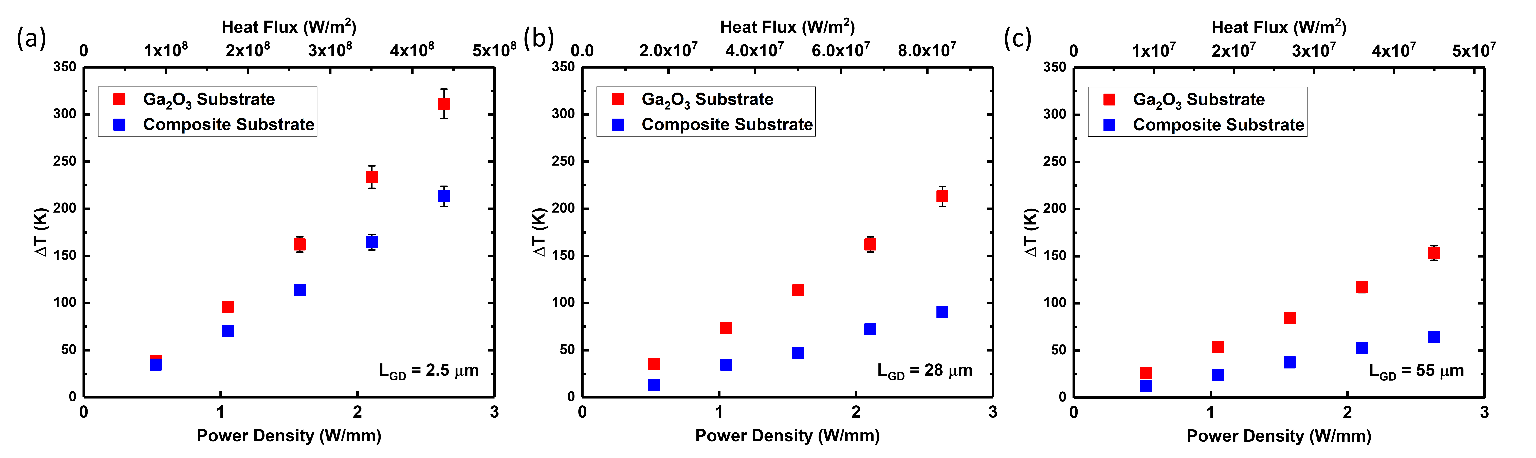

Nano-particle assisted Raman thermometry was used to perform in situ channel temperature measurement of the MOSFET structures. Anatase TiO2 nanoparticles of 99.98% purity were deposited on the devices to serve as surface temperature probes. The Stokes Raman peak shift of the Eg phonon mode was monitored during device operation to estimate the channel temperature rise. Measurements were taken on nanoparticles close to the drain side edge of the gate, where the channel peak temperature is expected to occur due to electric field and Joule heat concentrations. Measurements were performed on devices with different dimensions (LGD of ~2.2, 28, and 55 μm) fabricated on both the composite wafer and a native Ga2O3 substrate. Figure 3 shows the steady-state temperature rise (ΔT) as a function of power density and the corresponding heat flux values. When comparing the temperature rise for devices with different LGD, it is important to consider the heat flux since the area where Joule heating occurs is changing. Therefore, a device with a larger LGD will experience a lower temperature rise for a given power density. It should be noted that the devices on the composite and native substrates exhibited similar power densities for particular drain voltages (Vds). Due to the enhanced heat transfer performance of the composite substrate, a significant reduction in channel temperature rise (up to a 2.4× reduction) was observed for devices (especially those with larger LGD) operating under a power density of 2.63 W/mm.

Figure 3: Steady-state channel temperature rise of the MOSFETs fabricated on the composite substrate and a bulk Ga2O3 wafer. Devices with different LGD were tested. (a) LGD=2.5 μm, (b) LGD=28 μm, and (c) LGD=55 μm.

3. CONCLUSION

This work reports the fabrication of ultra-wide bandgap Ga2O3 power MOSFETs on a Ga2O3/4H-SiC composite wafer with simultaneous enhancement in the electrical and thermal performance. Low temperature (≤600°C) epitaxy and device fabrication processes were developed to preserve the structural integrity of the composite substrate. This enabled the first realization of (010)- oriented “homoepitaxial” Ga2O3 MOSFETs fabricated on a Ga2O3/4H-SiC composite substrate. The epitaxial Ga2O3-on-SiC MOSFETs exhibit a record high VBR (of up to 2.45 kV) and PFOM (~300 MW/cm2 ), both of which are highest among Ga2O3 FETs constructed on an heterogeneously integrated substrate to date. Under DC operation, a significant reduction in the channel temperature was achieved for the MOSFETs fabricated on the composite wafer as compared to devices homoepitaxially grown on a native Ga2O3 substrate. The experimentally measured temperature rise was validated by a 3D FEA electro-thermal model. Transient thermal analysis suggests that the cooling performance of an unoptimized composite wafer will be limited under high frequency switching operation. The theoretical cooling limit of using a hypothetical Ga2O3/diamond composite substrate with ideal heat transfer performance was assessed by modeling. A 10× improvement in thermal performance can be achieved by reducing the Ga2O3 layer thickness (to ~1 μm) and lowering the TBR at the Ga2O3/diamond interface (~7.8 m2K/GW). This work provides key guidelines for the fabrication and realization of high-power UWBG devices on a composite wafer that will enable to surpass the thermal limit of next-generation Ga2O3 power electronics.

搜索“华林科纳行业观察”小程序查看完整内容,或者加微信13358064333/18106288187。

上一篇: 超低损耗 Si3N4 的晶圆级加工

下一篇: 高密度铌酸锂光子集成电路