ABSTRACT

The chiplet architecture is one of the emerging methodologies andis believed to be scalable and economical. However, most currentmulti-chiplet systems are based on one uniform die-to-die interface,which severely limits flexibility. First, any interface has specificapplicable workloads/scales/scenarios; therefore, chiplets with auniform interface cannot be freely reused in different systems. Second, since modern computing systems must deal with complex andmixed tasks, the uniform interface does not cope well with flexibleworkloads, especially for large-scale systems.

To deal with these inflexibilities, we propose the idea of Heterogeneous Interface (Hetero-IF), which allows chiplets to use two differentinterfaces (parallel IF and serial IF) at the same time. Hetero-IF cancombine the advantages of different interfaces and cover up thedisadvantages of each, thus improving flexibility and performance.However, adopting hetero-IF-based multi-chiplet interconnectionsystems still faces many challenges. The microarchitecture, scheduling, interconnection, and routing issues have not been discussedso far.

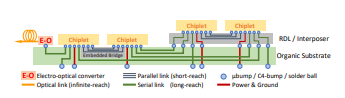

1 INTRODUCTIONChiplet has become one of the most popular VLSI design methodologies in recent years. With the support of advanced packaging andhigh-speed wireline technologies, multiple silicon dies can be integrated at high density and communication bandwidth. As shown in Figure 1, since 2.5D packaging provides abundanthigh-quality wiring resources, chiplets can be connected togetherthrough various die-to-die interfaces.Though there are multiple interface technologies with differentmetrics, most current multi-chiplet systems only choose one ofthem according to their major requirements. Variousgroups in the industry are pushing for some kind of technologyroute as a unified standard, however, we observetwo key inflexibilities caused by the uniform interface.

Figure 1: Multi-chiplet system: Advanced packaging technologies provide abundant interconnection possibilities.

Motivation 1. Chiplet reuse is limited by the uniform interface.Many studies have shown that huge cost savings can be achievedif identical chiplets are reused among multiple systems of differentscales. However, different scenarios and scales of systemshave different requirements for interfaces. Parallel interfaces suchas the Advanced Interface Bus (AIB) are low-latency and low-power,therefore applying to high-performance systems of small scales.However, since parallel interfaces are short-reach, even with expensive advanced packages, the system can only use flat topologiessuch as the 2D-mesh , which is insufficient for large-scalesystems because the diameter of the network is up to 𝑂(√𝑁).

Motivation 2. The Uniform interface is not flexible enough tohandle complex and mixed network traffic. For frequent “on-chip”communications such as the handshake, synchronization, and coherence protocols, low-latency parallel interfaces are more suitable . However, for heavy network traffic such as theall-reduce operation of large amounts of data, high-throughput andlong-reach serial interfaces are better choices. In modern high-performance systems, various network traffic patternsexist simultaneously. Choosing any kind of interfacemeans not being able to cope well with some workloads. Motivated by the limitations of the uniform interface, we propose theHeterogeneous Interface to deal with the inflexibility in differentscenarios. Nevertheless, building multi-chiplet systems throughheterogeneous interfaces faces many challenges.

2 BACKGROUND

2.1 Chiplet Architecture

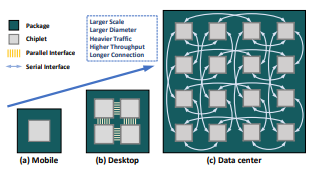

Another attractive feature of chiplet architecture is chiplet reuse.As shown in Figure 2, identical chiplets can be used to build multiplesystems of different scales. In this way, significant design costs canbe saved. Various works try to develop such scalable systemsthrough identical chiplets. These systems useidentical interconnect architectures at different scales. However,for different scenarios, systems of different scenarios and scaleshave different requirements for interconnection topologies andinterface metrics. For example, mobile systems require low powerconsumption, while datacenter systems require high throughput.Feng et al. present a scalable method to use different topologies fordifferent network scales. However, it only adopts the uniformserial interface, which limits the latency and energy performancefor small-scale systems and local communications.

Figure 2: Chiplet reuse in systems of different scales. Fordifferent scenarios, though using the same chiplet, systemshave very different integration and interconnection architectures.

2 BACKGROUND

2.1 Chiplet Architecture

The conventional VLSI system is implemented on a monolithicsilicon die. However, the die area is limited by the lithographicreticle, and designing large chips is very costly. In recentyears, packaging and high-speed wireline technologies have madegreat progress. Advanced packaging technologies provide a largeinterconnect base and a high volume of interconnection wires . Multiple chiplets can be interconnected and integrated at veryhigh density and communication bandwidth. Up to now, the vastmajority of current multi-chiplet systems still conservatively adoptflat topology such as 2D-mesh. Though flat topology is easy toimplement, it has limited network performance and does not fullyutilize the on-package interconnect resources.

3 ARCHITECTURE

3.1 Heterogeneous PHY

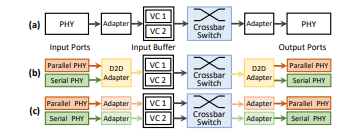

As shown in Figure 3(b), heterogeneous PHY is to replace the physical layer of the uniform interface with two different PHY. Theprotocol layer (adapter) above the physical layer is still uniform.From the perspective of the router, the ports are still the same astraditional uniform interfaces. Traffic through the heterogeneousPHY interface is handled by the die-to-die adapter at the protocollayer.

One of the advantages of heterogeneous PHY is that it is compatible with existing interconnection architectures. Since routers do nothave to be re-designed and there are few potential routing issues,the original multi-chiplet systems based on uniform interfaces canbe directly migrated and are not affected by the packaging technology. The use of heterogeneous PHY is also very simple, requiringonly the adapter to determine the distribution of traffic betweenthe two heterogeneous PHYs.

Figure 5: Heterogeneous interface architectures. (a) UniformInterface; (b) Heterogeneous PHY; (c) Heterogeneous Channel.

4 HETERO-CHANNEL: CASE STUDYAs

we illustrate in Sec 3, compared with the hetero-PHY interface, the hetero-channel interface is more flexible. However, usinghetero-channel interfaces still faces the routing challenge. Connecting several on-chip networks into a large interconnection canlead to serious deadlock and congestion problems. Extra channelsprovided by the hetero-channel interface introduce extra channeldependencies, which may lead to new deadlocks. Therefore, it isnecessary to clarify how to apply routing algorithms on the newhardware. To better illustrate our approaches, we use a specificinterconnection design as an example.

5 SUMMARY

The same as all architectures, the chiplet architecture also seeks generality. People have always expected one standard chiplet-tochiplet interface to cover all scenarios. However, it has been proven in practice that the uniform interface can significantly limit the chiplet architecture. Therefore, we propose and discuss a new architecture: Heterogeneous Interface, which makes multi-chiplet systems more flexible. In general, flexibility is reflected in three aspects:

Flexibility in interconnection. First, since the connection is no longer limited by the physical properties of the interface, the topology of multi-chiplet networks can be more flexible. Second, there is richer path diversity for hetero-IF-based networks, which improves the network performance under complex traffic.

Flexibility in scheduling. Heterogeneous interfaces allow different packets to go through different physical channels at different times, which greatly enhances the flexibility of system scheduling. By rule-based or application-aware scheduling policies, better metrics are achieved.

Flexibility in economy. First, the choice of packaging options can be more flexible, meaning that the appropriate package can be selected based on cost constraints. Second, the application scope of chiplets has been expanded, meaning that more systems can be composed with fewer chiplets, which has proven to be economical.

In this paper, two typical implementations of heterogeneous interfaces and their usages are discussed. The overheads are analyzed, and a few practical scheduling methods are introduced. Also, interconnection and routing methods for hetero-IF-based networks are presented and discussed. Extensive evaluations demonstrate that hetero-IF does deliver significant performance improvements and flexibility gains.