Crystalline silicon solar cells with regular rigidity characteristics dominate the photovoltaic market, while lightweight and flexible thin crystalline silicon solar cells with significant market potential have not yet been widely developed. This is mainly caused by the brittleness of silicon wafers and the lack of a solution that can well address the high breakage rate during thin solar cells fabrication. Here, we present a thin silicon with reinforced ring (TSRR) structure, which is successfully used to prepare free-standing 4.7-μm 4-inch silicon wafers. Experiments and simulations of mechanical properties for both TSRR and conventional thin silicon structures confirm the supporting role of reinforced ring, which can share stress throughout the solar cell preparation and thus suppressing breakage rate. Furthermore, with the help of TSRR structure, an efficiency of 20.33% (certified 20.05%) is achieved on 28-μm silicon solar cell with a breakage rate of ~0%. Combining the simulations of optoelectrical properties for TSRR solar cell, the results indicate high efficiency can be realized by TSRR structure with a suitable width of the ring. Finally, we prepare 50 ~ 60-μm textured 182 × 182 mm2 TSRR wafers and perform key manufacturing processes, confirming the industrial compatibility of the TSRR method.

Photovoltaics plays a leading role in achieving the goal of a low-carbonemission society. Nowadays, crystalline silicon (c-Si) solar cell dominates the photovoltaic (PV) market, with a market share of over 95% owing to their high module efficiencies, long lifespan of more than 25 years as well as high abundance of silicon. Among them, there is a huge market potential for lightweight and flexible thin c-Si solar cells since they can be integrated with buildings, remote power applications such as electric vehicles and aircrafts and wearable electronic devices3 . However, they are not yet widely used due to the mechanically brittle nature of c-Si and the dramatically increasing trend in breakage rate during cell processing as the thickness of the wafer decreases.

For the above reason, there is a trade-off between thickness and area for thin silicon solar cells. It is very challenging to prepare thin c-Si solar cells with large areas to a very thin thickness. Table 1 summarizes the characteristics of c-Si solar cells with a thickness of ≤ 40 μm reported since 2010. We can see that the vast proportion of the solar cells has an active area of less than 4 cm2 , and some of them even have an area of less than 0.03 cm2 . At present, the most straight-forward and low-cost route for preparing thin silicon (solar cells) is to process them in a free-standing way, as is done for standard wafers. However, in 2016, CEA-INES reported a drastic increase in the breakage rate from about 10% at 100 μm thickness to a terrible ~96% at 70 μm thickness in their silicon heterojunction (SHJ) pilot line (using 156 × 156 mm2 pseudo-square wafers). Even though process and handling adjustments were implemented, a breakage rate of up to 4.5% during the fabrication of 100 μm thick high-temperature diffused junction cells in the pilot production line of Hanwha Q CELLS was reported7 . Such high breakage rates lead to unacceptable yield losses and high total production costs. A solution to this fragility is to prepare thin silicon based on a parent substrate, such as epitaxy, spalling, ‘epifree’, silicon-oninsulator (SOI, ‘smart-cut’ process) and micro-machining (Table 1), and some of them require further bonding or transferring of the thin silicon to external supporters to cope with the following solar cell preparation process. Nevertheless, these fabrication processes are too complicated, leading to questions about the viability of these processes for fabricating thin silicon solar cells in a cost-effective way at an industrial scale. Moreover, the thin silicon with hard substrate is not flexible, which limits its range of applications. The challenges of freestanding and supported processing of thin silicon remain to be answered.

Results

Preparation of TSRR structure

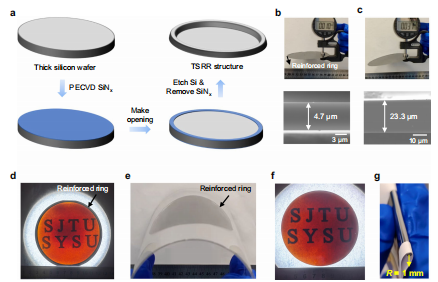

Figure 1a shows preparation process for the TSRR structure. Generally, thick silicon wafers are etched into ATS wafers with desired thickness by alkaline solutions such as Potassium hydroxide (KOH) and Tetramethylammonium hydroxide (TMAH). However, the ATS structure is easily broken down during thin silicon solar cell fabrication, and it is important to note that it is not possible to prepare thinned 4-inch wafers with a thickness of <10 μm with ATS structure based on our experiments. We proposed a method to fabricate the TSRR structure, which requires only 3 more steps with common devices in photovoltaic factories for mass production: first depositing 70 nm silicon nitride (SiNx) on both sides of the normal thick silicon wafers by plasma enhanced chemical vapor deposition (PECVD) or low pressure chemical vapor deposition (LPCVD), then removing the SiNx from the central region of one side using a die, laser or photolithographic to make opening, and finally etching the wafer in alkaline solution to the desired thickness. Thanks to the protection of SiNx layer, the silicon in the edge region of the wafer maintains its original thickness, thus forming a reinforced ring. Figure1b (top) displays a thinned 4-inch wafer with TSRR structure being measured by a handheld thickness gauge (reading 10μm), its real thickness is 4.7 μm, as depicted in Fig. 1b (bottom), which is the scanning electron microscope (SEM) image of the cross section. The width and thickness of the reinforced ring are 2 ~ 4 mm and 192 μm, respectively. To the best of our knowledge, this is the largest area of free-standing monocrystalline silicon with a thickness of <5 μm reported so far. Figure1c (top) displays the corresponding measurement (reading 31 μm) by handheld thickness gauge of the thinned 4-inch wafer with ATS structure, and its exact thickness is 23.3 μm as shown in Fig. 1c (bottom). We can find that the thinned 23.3-μm wafer with ATS structure is bending downward under gravity only. However, this flexibility is not desired in the processing or testing stages, as it tends to cause breakage. In contrast, the 4.7-μm thin silicon wafer with reinforced ring still remains horizontal under gravity, demonstrating the supporting role of the reinforced ring. We also offer the SEM image about the boundary of the reinforced ring and the central thin silicon region in Supplementary Fig. 1.

Fig. 1 | Preparation and performance demonstration of the thin silicon with reinforced ring (TSRR) structure.

Figure 1d is the optical image of the 4.7-μm 4-inch wafer with TSRR structure underneath white light illumination, the letters “SJTU, SYSU” on the paper below the thin silicon wafer are clearly visible, which reflects its ultra-thinness and high red light transmission10. At the same time, based on the color uniformity shown here, we can also see that the thickness of the wafer is fairly uniform, and according to our further quantitative measurements on the thickness uniformity, as demonstrated in Supplementary Fig. 2, the TTV for this thin silicon preparation method is within 6 μm. Despite of the thick reinforced ring, it is still bendable, as exhibited in Fig. 1e. And its flexibility depends on the combined bending performance of the reinforced ring and the central thin silicon region. This means that we can control the flexibility of the entire wafer by adjusting the thickness of the reinforced ring. If high bending performance is required, we can cut off the reinforced ring with a laser in the last process step. Figure 1f shows a fully thin wafer with an area of 60.8 cm2 obtained in this way. And it has a bending radius of 1 mm as revealed in Fig. 1g.

Fig. 2 | Stress analysis for thin silicon wafers with ATS and TSRR structures in three cases during fabrication process in which the breakage rates are very high.

In addition, it is important to emphasize that, studies have shown that the cracking starts at the edge of the wafer and breakage occurs due to crack propagation, and Wieghold et al., discovered that the critical force required to break a wafer decreases as thickness decreases based on their simulations of edge micro-crack propagation in wafers with different thicknesses, which implies the quality of the edges of the wafer is critical especially for thin wafer. Fortunately, our proposed thick reinforced ring of TSRR structure enables edges reinforcement of thin silicon wafer, which means that the reinforced ring not only shares the stress but also raise the critical force of breakage for thin silicon wafer.

We start by looking at the first group of ATS structure, during the thinning process, i.e., thinning silicon from 250 μm to 21 ~ 29 μm with alkaline solution, 7 samples broke. Followed by 9 samples broke during texturing and 1 sample was fragmented during handling and transferring between the two processes. Surprisingly, the breakage rate was as high as 85% after just these two wet process treatments. We can conclude that the wet processing step is crucial for ultra-thin (<30 μm) silicon wafers, and we need to be careful in order to minimize the breakage rate. In some solar cell preparation processes, vacuuming and taping are required. The numbers of breakage for both processes were 1, but note that at the beginning of taping, there was only one sample left, as there was 1 sample breakage in handling and transferring between them. Therefore, it can be concluded that the breakage rate is >85% for fabricating 21 ~ 29 μm solar cells with an area of 2.4 × 2.8 cm2 using ATS structure. Breakage rate can even increase to 100% if vacuuming and taping are required in the fabrication. As the thickness increases to 51 ~ 57 μm, the breakage rate decreases to 40% for ATS structure. In sharp contrast, the breakage rates of both 19 ~ 23-μm and 42 ~ 50-μm groups were 0% for TSRR structure. The aforementioned results prove that the reinforced ring of TSRR structure can greatly reduce the breakage rate during the preparation of thin silicon solar cells.

Then we successfully performed screen printing at 170 °C using low-temperature silver paste on 60-μm textured TSRR wafers as shown in Fig. 5b. And its flexibility performance is demonstrated in Fig. 5c. The breakage rate during this process is 0% (0/5). We should admit that there are finger interruptions at the boundary of the reinforced ring and the central thin silicon region because of the steep slopes there. This may require further optimization of screen printing or development of new metallization methods such as metal plating44. We think this is acceptable since this is the world’s first attempt at a manufacturing process for this kind of thin structure, and there are still some processing details to be worked out together. What’s more, if we prepare IBC solar cells whose back side is flat as shown in Fig. 3a, or if we decide to use this thin silicon structure with the reinforced ring cut off when it comes to applying it in some scenarios, the finger interruptions will be no longer an issue.

Discussion

In summary, we present a TSRR structure, which requires only 3 more steps with common devices in photovoltaic factories for mass production, and free-standing 4-inch 4.7-μm crystalline silicon wafer (Ratio ≈ 3%) was successfully prepared by this method. This is the largest area of free-standing monocrystalline silicon with a thickness of <5 μm reported so far based on our knowledge. Then with the help of COMSOL Multiphysics, we investigated the mechanical properties of TSRR structure and ATS structure under three cases, and the simulation results revealed that the reinforced ring of TSRR structure can share a large stress when subjected to external forces, thus making the central thin silicon region of TSRR structure bear a smaller force compared to ATS structure. We further prepared solar cells with TSRR structure and obtained an efficiency of 20.33% (certified 20.05%) on 28-μm silicon solar cell with all dopant-free and interdigitated back contacts, which is the highest efficiency reported for thin silicon solar cells with a thickness of <35 μm. Meanwhile, the breakage rate of each process of solar cell fabrication with both structures were tracked. The results demonstrated that the breakage rate of 21 ~ 29-μm group with an area of 2.4 × 2.8 cm2 was 85% ~100% for ATS structure, while the breakage rate of 19 ~ 23-μm group with a whole area of 2.4 × 2.8 cm2 was 0% for TSRR structure. The above simulations and experiments confirmed that the reinforced ring can provide support throughout the solar cell preparation process and thus greatly suppressing the breakage rate. Then, based on TCAD numerical simulations, we investigated the carrier transport mechanism of the solar cell with TSRR structure, and the impact of thickness of the central thin silicon region and the width of the reinforced ring on the solar cell performance, which suggested that the value of Ratio should ideally be less than ~10% to maintain high efficiency. Finally, we prepared 50 ~ 60-μm textured TSRR wafers (Ratio = 8.2%) based on 182 × 182 mm2 pseudosquare wafers with an original thickness of 150 μm, and then performed screen printing, high-temperature and wet manufacturing processes, which confirms the industrial compatibility of TSRR structure. We believe that this TSRR method is a feasible solution for the mass production of thin silicon solar cells.