Keywords: Wafer cleaning, surface preparation, wet etch, scaling, semiconductor trends

Abstract. The semiconductor industry is undergoing a transition driven by end use markets. In recent years, mobile devices have been the leading generator of growth. Now the connection of various products and machines to the internet is generating new and extensive demands for memory (storage of the data), logic (intelligent processing of the data including machine learning), and sensing (e.g., image sensors generating visual data). Thus the versatile planar MOS transistor based semiconductor technology has diverged into various specialized and complex branches, with each technology type using unique approaches to address scaling challenges. These lead to specific requirements for semiconductor wafer surface preparation. This paper will review the high level industry trends and how they affect surface preparation specifically.

Introduction The world is continually being transformed by information handling systems that are enabled by semiconductors and the speed of their ongoing development. In turn, innovative and empowering applications are driving semiconductor technology development to continually overcome difficult barriers. With over half the world now connected to the internet [1], connectivity has begun expanding to various devices and machines transferring data and remotely storing it. With the expansion of this Internet-of-Things (IoT), many new and exciting capabilities are emerging. These include Virtual, Augmented, and Mixed Reality (VR/AR/MR), Artificial Intelligence (AI), autonomous driving, machine learning, Robotic Process Automation (RPA), and Blockchain. Associated massive amounts of generated data require fast local data reduction processing in combination with high volumes of memory storage, while high performance is required for machine learning and applications requiring minimal lag times (latency) such as autonomous driving and assisted surgery.

The overall semiconductor market has been expanding in support of these emerging demands. Historically, from 1986 through 2017 this market has had a compound annual growth rate (CAGR) of 9%, becoming a $378B market in 2017. Even a more modest CAGR of 5% to 7% over the next 40 years would take it to $2.6T to $5.6T by 2057 [2]. As this market has matured in recent years the leading edge of semiconductor development has divided into a range of specific technology types, each having unique requirements. Enabling the various key functions in support of current and emerging end use applications are DRAM (working memory), NAND (information & data storage), MPU logic (supporting AI), and various sensors and actuators (e.g., CMOS Image Sensors, the visual component of automation). Dramatic growth in demand for memory has occurred, driven in large part by graphic and video applications in recent years [3]. The increase in photos taken every year is exponential, with a hundred billion more taken in 2017 than in 2016 (about 85% of these by smartphones) [4]. This trend is expected to continue. Figure 1 shows the associated high CAGR forecasted for memory revenue relative to other types of semiconductors over the years 2017 – 2022 [5]. This paper will review the evolution from planar technology to increased use of the third dimension in current semiconductor technology, and its relation to cleaning and surface preparation.

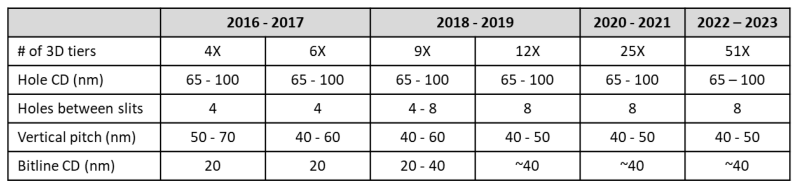

Table I: Scaling trend of 3D NAND devices by generation (adapted from reference [11]).

Critical Issues for Clean and Wet Etch

The described trends in semiconductor manufacturing have led to the following major needs for wet etch and clean: control of stiction driven pattern collapse, specialized selective etch and clean processes, increased attention to the wafer bevel, and defect removal without pattern damage or material loss. Pattern collapse is a major challenge due to the aggressively increasing aspect ratios of structures. When liquid is removed from patterns after wet etch or clean, the pressure difference between the receding liquid and the gas (Laplace pressure) generates a force that increases as the liquid surface tension increases and as the spacing between patterns decreases [18, 19]. Minimizing the surface tension by liquid isopropanol (IPA) drying in single wafer spin systems has historically been used, but eventually becomes ineffective as pattern spacing decreases and aspect ratio increases. More recently, chemical additives have been introduced after the DIW rinse step, to adjust the contact angle. The method has proven effective to suppress pattern collapse at higher aspect ratios compared with IPA drying [19]. Furthermore, by lowering the surface energy, surface treatments can keep the adhesion force lower than the elastic restoring force of the pattern [20]. However, increasing aspect ratios continue to pose challenges especially in memory, and particularly for capacitor structure mold removal and STI post etch cleaning. A more robust solution can be provided by using Supercritical CO2 (SCCO2) to dry patterned wafers, with the drying medium having zero surface tension [21, 22]. While SCCO2 appears to have the most potential for extendibility among known methods, it has been pointed out that at extreme aspect ratios random thermal vibrations can cause long patterns to touch and potentially collapse, suggesting a possible fundamental limit regardless of processing method [23].

上一篇: 半导体湿式蚀刻和表面制备的工业背景

下一篇: 电化学行为后的蚀刻清洗