There are a number of materials considered for various processes in 3D integration. These materials are critical to the development of key processes, such as through-strata-via (TSV), wafer and chip bonding, and wafer handling. This paper reviews the recent advances of some variable materials and processes, compares their advantages and technical challenges, and discusses the options towards full 3D-TSV integration.

Introduction

The semiconductor technology has been one of the most powerful technologies in the last half century, which has advanced exponentially following the famous Moore’s Law [1]. From the single core microprocessor (CPU), to dual-, quad-, now hexa-core, as well as demonstration of 48 and 80 cores, in addition to graphic processing unit (GPU) of 256 cores or more, the semiconductor technology is more than powerful enough for many applications. On the other hand, fast pace technology development has been pushing for “More than Moore” applications with functional diversifications, such as analog/RF, HV power/energy, passives, sensors/actuators, biochips and bio-medical devices [1]. The key technology has been the so called system-inpackage (SiP). It is a clear that we will develop the technologies for system-level applications, so we can combine information processing with many real world applications.

Moreover, due to physical, technical and economic limitations, most semiconductor practitioners today have concluded that CMOS shrinkage following Moore’s law will come to an end soon, probably before 2020, and that 3D integration is one of the few avenues available to alleviate this problem and to facilitate the “More than Moore” (heterogeneous) integration. 3D hyper-integration is to vertically stack and interconnect heterogeneous materials, technologies and functions (Fig. 1) [2]. The potential benefits of 3D integration can vary depending on approach; they include multi-functionality, increased performance, increased data bandwidth, reduced power, small form factor, reduced packaging, increased yield and reliability, flexible heterogeneous integration, and reduced overall costs [2-10]. This 3D technology can enhance system performance with existing/best materials, process technology, and fabrication facilities for each stratum, continuing the legend of semiconductor technology of smaller, faster and cheaper, and now smarter! 3D technology provides the viable path to future paradigm combining the semiconductor technology with “More than Moore” applications, thus future smart systems can easily interact with people and environment.

There have been several key roadblocks to 3D integration:

• Creation of right 3D technology platforms

• Innovations of key 3D processing technologies

• Development of 3D infrastructure (equipment, ECAD tools and standards)

• Simulation and modeling of the performance of 3D integrated systems • Reliability, yield, and cost.

Many solutions and technologies have been investigated to overcome these roadblocks [1-32]. Semiconductor industry has been focusing on the low hanging fruit using 3D technology, i.e., image sensors (already in the market [7, 11]), wide I/O (high data bandwidth) applications (e.g., 3D memory stack for mobile applications [8-9, 14, 23- 25]), and 3D integration of memory and processor for high performance computing [2-7, 15-18, 28]. There are still technology challenges ahead now with these low hanging fruit applications, and in future with high functionality systems.

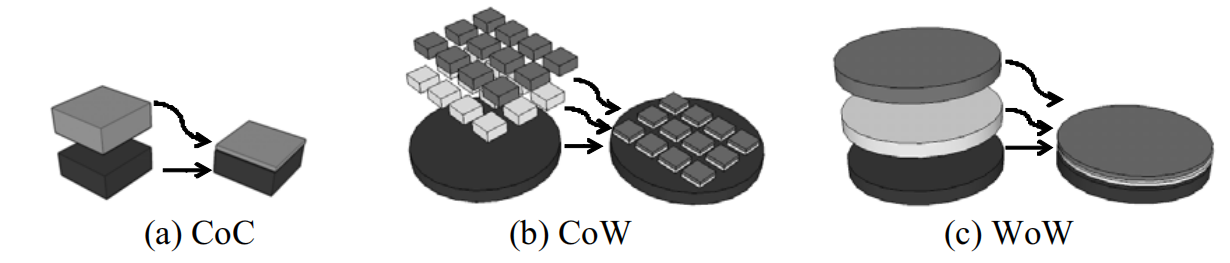

This paper attempts to provide an overview on advances in materials and processes for 3D-TSV integration technologies, particularly on TSV, inter-strata bonding, wafer thinning, and alignment. There are a variety of choices for materials (e.g., conductors, substrate, interposer, low-k dielectric compatible materials, integrated passives and underfill) and processes (TSV, stacking, bonding, wafer thinning, thin wafer handling, and self-assembly). The choices can vary, depending on the 3D integration technology platforms of chip-on-chip (CoC), chip-on-wafer (CoW) or wafer-on-wafer (WoW) as shown in Figure 2. Since current research and development for 3D products focuses on 3D technologies, this paper discusses the advances in materials and processes based on the key 3D technologies, while variations on 3D platforms are addressed accordingly.

Figure 2

TSV Processes and Materials

TSV is the core element for current 3D integration technologies and can be used for all the CoC, CoW and WoW technology platforms. The TSV technologies have been intensively developed by universities, research institutes, government laboratories and semiconductor companies [2-35]. In particular, semiconductor consortia, foundries and semiconductor companies recently made tremendous progress towards volume manufacturing for, as a near-term product, wide I/O 3D-DRAMs [8-10, 14, 16, 20-28].

上一篇: 硅微加工的HF溶液中的电化学刻蚀

下一篇: 3D集成技术:现状及应用发展