Abstract

Thermal performances of 3D IC integration system-in-package (SiP) with TSV (through silicon via) interposer/chip are investigated based on heat-transfer and CFD (computational flfluid dynamic) analyses. Emphases are placed on the determination of (1) the equivalent thermal conductivity of interposers/chips with various copper-fifilled, aluminum-fifilled, and polymer w/o fifiller fifilled TSV diameters, pitches, and aspect ratios, (2) the junction temperature and thermal resistance of 3D IC SiP with various TSV interposers, (3) the junction temperature and thermal resistance of 3D stacking of up to 8 TSV memory chips, and (4) the effect of thickness of the TSV chip on its hot spot temperature. Useful design charts and guidelines are provided for engineering practice convenient.

Introduction

Moore’s law (emphasizes on minimum costs and innovations) has been the most powerful driver for the development of the microelectronic industry. This law focuses on lithography scaling and integration (in 2D) of all functions on a single chip, perhaps through system-on-chip (SoC). On the other hand, the integration of all these functions can be achieved through system-in-package (SiP) or, ultimately, 3D IC integration SiP. There are many critical issues of 3D IC integration [1–30], e.g., EDA (electronic design automation) softwares are not commonly available; test methods and equipments are lacking; knowngood-die (KGD) are required; fast chips mixed with slow chips; large chips mixed with small chips; microbumps usually are required; equipment accuracy for alignments; wafer thinning and thin wafer handling during processes; thermal management issues; 3D inspection issues; 3D expertises, infrastructure, and standards are lacking; TSVs usually are required for 3D IC integration; TSV cost is higher than wirebonding; TSV high-volume production tools are lacking/expensive; TSV design guidelines are not commonly available; TSV design softwares are lacking; TSV technology usually requires microbumps; test methodology and softwares of TSV are lacking; copper fifilling helps on thermal but increases TCE (thermal coeffificient of expansion); copper fifilling takes a long time (low throughputs); the tough requirements of TSV wafer yields (>99.9%); TSV wafer warpage due to TCE mismatch; thin TSV wafer handling during all the processes; TSV with high aspect ratios are diffificult to manufacture at high yield; TSV inspection methodology; TSV expertises, infrastructure, and standards are lacking.

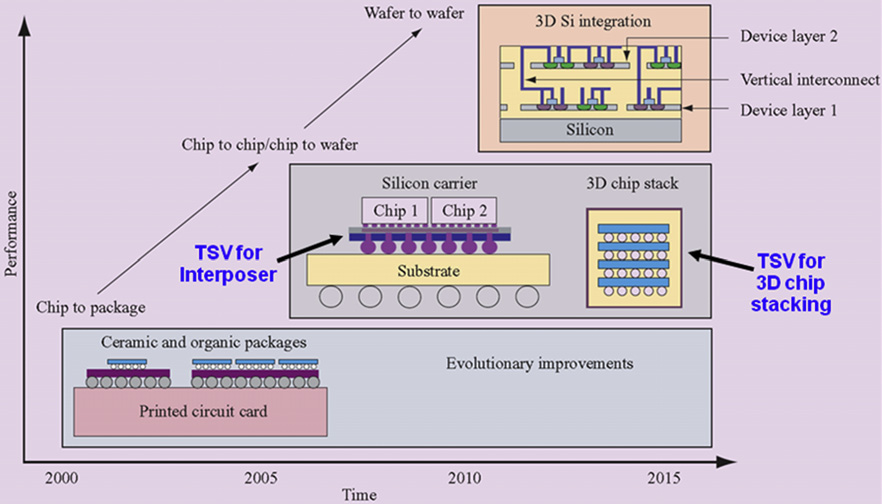

Fig. 1 shows the generic 3D technology roadmap for high -performance computing systems given by IBM [1]. It can be seen that in the next few year, TSV is used to stack up chips such as memories and TSV interposer is needed for supporting high-performance chips. The key function of this TSV interposer is to fanout the very fifine-pitch and high pin-count pads (circuitries) of the high performance chips with redistribution layers either on the top or bottom or both of the TSV interposer.

Fig 1

As mentioned, thermal management is one of the critical issues of 3D IC integration. This is because: (1) the heat flflux generated by stacked multifunctional chips in miniature packages is extremely high; (2) 3D circuits increase total power generated per unit surface area; (3) chips in the 3D stack may be overheated if cooling is not properly and adequately provided; (4) the space between the 3D stack may be too small for cooling channels (i.e., no gap for flfluid flflow); and (5) thin chips may create extreme conditions for on-chip hot spots. Thus low-cost and effective thermal management design guidelines and solutions are desperately needed for widespread use of 3D IC integration SiP.

In this study, based on the theory of heat transfer, the thermal performances of high-performance packages with TSV interposers and memory chip stacking are studies. The results are plotted in useful design charts for engineering practice convenient and design guidelines are also provided.

Even with the most advanced softwares and high-speed hardwares, it is impossible to model all the TSVs in a 3D IC integration SiP. In this study, equivalent thermal conductivity of a TSV interposer/chip with various TSV diameters, pitches, and aspect ratios (as shown in Fig. 2) are developed fifirst through detailed 3D heat transfer and CFD analyses [31–34]. These equivalent thermal conductivities are then used (with the TSV chip/interposer as a block) to perform all the simulations reported herein.

上一篇: 湿法蚀刻MEMS硅腔的工艺控制