I. INTRODUCTION

It is estimated that the coming 5G network will connect more than 100 billion devices and deliver fast radio frequency (RF) data communication with high bandwidth and low latency among these devices. This will have profound impact on a variety of fields, including computing, communication, consumer, industrial, medical and automotive. A high performance, low cost yet reliable packaging solution is a key enablement for the wide adoption of 5G.

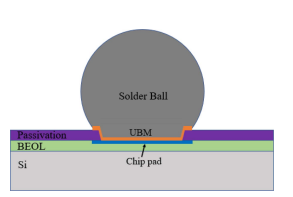

Wafer level chip scale package (WLCSP) is a workhorse in advanced packaging in recent years [1]–[2]. Fig. 1 shows a schematic of the WLCSP chip/bump build-up crosssection, where a solder ball directly landed on a chip pad via a UBM (under bump metallization) layer. The chip pad is typically an Al pad fabricated during wafer back end ofline (BEOL) process. A passivation layer, which is typically polyimide-based material, is also deposited on top of the chip BEOL. Such configuration with bump landing on chip pad is referred as BOP (bump on pad). Alternatively, the connection between solder bump and chip can be through a redistribution layer (RDL) or multiple RDLs. The bumped chip is then directly attached to a printed circuit board (PCB) without using a substrate in between.

WLCSP is suited for the RF applications that 5G is targeting at. The 5G rollout starts with sub-6GHz and is to be followed by millimeter wave (mm-Wave) band. In these frequency ranges, especially in mm-Wave, one great challenge is the free space loss of the radiated signal power. The direct chip-to-board attach through solder joints in WLCSP provides low interconnect inductance and resistance.

This results in greatly reduced package parasitics and signal loss. To further mitigate the RF signal loss, high gain antenna arrays with power amplifiers, which also dissipate significant amount of heat, are often employed [3]. The direct chip-to-board connection of WLCSP also improves the package thermal performance which is critical to 5G RF applications. WLCSP also offers the smallest package footprint with true chip scale package, which is beneficial to applications such as mobile, wearable and IoT. Furthermore, the elimination of package substrate in WLCSP reduces the cost, which is essential for adoption at scale.

II. TEST VEHICLE

Dedicated test chips were used for this WLCSP work. TABLE 1 lists four test vehicles based on two test chips: D1 and D2 [10]. The area of D1 and D2 are 3.4 mm by 3.4 mm, and 3.6 mm by 3.6 mm, respectively. The die used in TV3 is 80 µm thinner than other TVs. All chips use full flow FEOL and BEOL processes. Two BEOL stacks S1 and S2 are used. Stack S1 has 10 Cu metal levels with a 2 µm thick Al. Stack S2 has 7 Cu levels and with a 4 µm thick Al. Both stacks have low k dielectrics, whereas S1 also has ULK layers. The k value of S1 ULK is 2.45 which is even lower than the ones used in most advanced nodes. This low k value boosts electrical performance and reduces the power consumption, but with increased CPI risk.

The dedicated test structures on the test chips include chip perimeter lines, perimeter via stacks, under bump serpcombs, under bump via stacks, individual corner bump stitches & stitch pairs, and bump daisy chains. The test structures were used to detect structural integrity fails and moisture ingress related degradation. ESD protection circuits were also designed for the ESD sensitive test structures. The test structures have a wide test coverage and these structures had also been placed at CPI critical locations which include, the corner bumps, the die corners and the peripherals, and the under bump BEOL stacks.

III. COMPONENT LEVEL RELIABILITY

To ensure the dies have no intrinsic reliability issue, a component level reliability (CLR) test was first conducted on dies with bumps. TV1 and TV2 were used for this component level reliability test. Standard JEDEC environmental stresses, including temperature cycling (TC, condition B), unbiased HAST (uHAST), high temperature storage (HTS, 150◦C), were used for this reliability evaluation. Prior to each stress tests, a MSL1 (moisture sensitivity level 1) preconditioning (pre-con) was also applied to all parts. The details of the stress conditions are listed in TABLE 2. Both TV1 and TV2 passed all CLR tests. These tests verify that the test chips after bumping are intrinsically robust.

Fig1

A perhaps even more difficult challenge is solder joint reliability (SJR). The CPI thermo-mechanical stress can cause crack generation and growth in solder joints and eventually fail the interconnect. In RF applications, smaller bump size is preferred for improved performance. In many cases, a fairly large percentage of chip area is depopulated with solder bumps to further reduce the coupling noise. These two requirements can significantly impact the reliability life of the solder bumps even for small chip applications.

The dedicated test structures on the test chips include chip perimeter lines, perimeter via stacks, under bump serpcombs, under bump via stacks, individual corner bump stitches & stitch pairs, and bump daisy chains. The test structures were used to detect structural integrity fails and moisture ingress related degradation. ESD protection circuits were also designed for the ESD sensitive test structures. The test structures have a wide test coverage and these structures had also been placed at CPI critical locations which include, the corner bumps, the die corners and the peripherals, and the under bump BEOL stacks.

III. COMPONENT LEVEL RELIABILITY

To ensure the dies have no intrinsic reliability issue, a component level reliability (CLR) test was first conducted on dies with bumps. TV1 and TV2 were used for this component level reliability test. Standard JEDEC environmental stresses, including temperature cycling (TC, condition B), unbiased HAST (uHAST), high temperature storage (HTS, 150◦C), were used for this reliability evaluation. Prior to each stress tests, a MSL1 (moisture sensitivity level 1) preconditioning (pre-con) was also applied to all parts. The details of the stress conditions are listed in TABLE 2. Both TV1 and TV2 passed all CLR tests. These tests verify that the test chips after bumping are intrinsically robust.

上一篇: 用于微波功率应用的碳化硅

下一篇: 用于5G应用的后处理多孔硅